Part Number: PGA305EVM-034

I have PGA305EVM-034.

This is my first time with this system.

I am trying to setup a gain.

PGA305EVM-034 is setup for:

1. Voltage output

2. OWI

3. P_GAIN = 5

4. P_INV = NO

5. V_BRG = 2.5V

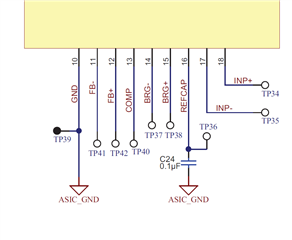

6. External Bridge 4.89K, $4.99K, 4.99K & 4.99K

==> Reading P_ADC = FFFEB1A

Changing only

P_INV = YES

==> Reading P_ADC = FFFEAF0

Both reading are negative number.

If I changed gain polarity, should the reading change sign?

Question:

How do I calculate PADC digital reading from Bridge Values and Setting of the system (P_GAIN, P_INV, V_BRG)

Did Change Bridge values correctly by entering new Potentiometer value?

Thank you for your help.

Regards,

Igor