Hello,

We would like to ask about the internal polling rate of the PADC in the PGA900.

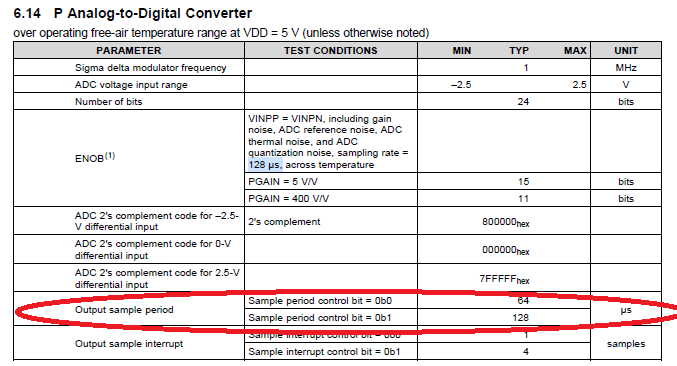

Looking through the datasheet and it seems to only mention the output I2C rate, but not how fast the PGA900 itself samples the analog signal at.

Could you please let us know? Thank you, Keith