Dear TI Experts,

I am a bit confused by dstBIdx being set to zero in SDK DPU file rangeprocdsp.c.

In the rangeprocdsp.c source code file, located at <install_dir>\mmwave_sdk_03_06_00_00-LTS\packages\ti\datapath\dpu\rangeproc\src

Here is the code, starting at line 172:

syncACfg.aCount = dpParams->numAdcSamples * BYTES_PER_SAMP_1D; syncACfg.bCount =MAX(dpParams->numRxAntennas / 2U, 1U) * dpParams->numChirpsPerChirpEvent; syncACfg.srcBIdx = rangeProcObj->rxChanOffset * 2U ; syncACfg.dstBIdx = 0U;

For 4 RX antennas, this works out to

syncACfg.bCount = 2;

Does this mean that the second B array is overwriting the first B array in the destination buffer?

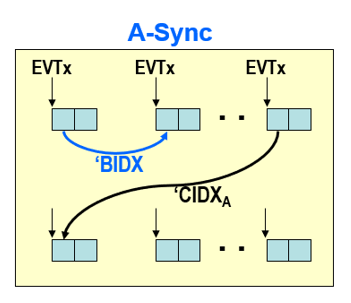

sprugs5b Keystone Architecture EDMA3 Controller gives an example of SRCBIDX being set to 0, and says on page 33, section 2.3.2.8, "SRCBIDX = 0000h (0): no address offset from the beginning of an array to the beginning of the next array. All arrays are fixed to the same beginning address." It goes on to say that the we should refer to the SRCBIDX examples for DSTBIDX.

Can you help me understand what it means that dstBIdx is set to zero?

Thank you for your help.