HI. TI

As the application size increases while using 1843AOP,

It has become impossible to store data using only R4F's TCMB (ori:0x0800_0000, len:0x0002_FFFF) Data RAM.

Therefore, an exception occurs after moving the statically allocated .bss (global variables) area to L3 memory.

There is some randomness in the occurrence cycle, but it generally occurs within 3 seconds after successfully executing the sensorStart command.

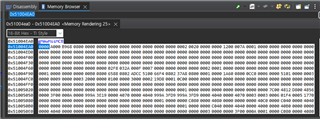

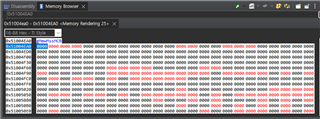

As a result of debugging in the EVM kit environment through *.map files and CCS Memory Viewer,

we confirmed that all .bss areas moved to L3 were initialized to 0 when abort() occurred.

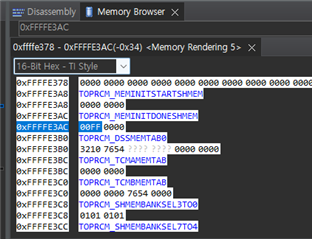

before abort() occurs :

after abort() occurs: (frame count : 17)

(2) https://www.ti.com/lit/ug/swru520e/swru520e.pdf?ts=1712213767734#page=1548

(3) https://www.ti.com/lit/ug/swru520e/swru520e.pdf?ts=1712213767734#page=1136

By referring to the links above, I found out that it may be related to the 'SHMEMBANKSEL' register.

Related code to set TOPRCMRegs(MSS_TOPRCM) appears to be in SDK/ti/drivers/soc,

but TOPRCMRegs::SHMEMBANKSEL3TO0 and TOPRCMRegs::SHMEMBANKSEL7TO4 I couldn't find the code to set it.

Since the problem I am experiencing is initialization while running the application,

it may be different from the case in link (1),

but it is difficult to judge because the technical manuals in links (2) and (3) are not detailed enough.

Is this a problem that needs to be corrected by writing the code that controls SHMEMBANKSEL?

Or is it a different problem with some other factor that could cause the memory to be initialized?

we plan to set up the MPU region to check if there is anything incorrectly accessed inside R4F.

here is my r4f_linker.cmd

/*----------------------------------------------------------------------------*/

/* r4f_linker.cmd */

/* */

/* (c) Texas Instruments 2016, All rights reserved. */

/* */

/* USER CODE BEGIN (0) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Linker Settings */

--retain="*(.intvecs)"

/*----------------------------------------------------------------------------*/

/* Memory Map */

/* 1843 L3 : ADDR:0x5100_0000 ~ 0x511F_FFFF */

/* MMWAVE_L3RAM_NUM_BANK : 8 */

/* MMWAVE_SHMEM_BANK_SIZE : 0x00020000 */

/* MMWAVE_MSSUSED_L3RAM_SIZE : 0x000A0000 */

/* MMWAVE_MSSUSED_L3RAM_CODESIZE : 0x00010000 */

/* MMWAVE_L3RAM_SIZE : 0x00060000 */

/* MMWAVE_L3RAM_DATA_SIZE : 0x00090000 */

#define MMWAVE_L3RAM_SIZE (MMWAVE_L3RAM_NUM_BANK*MMWAVE_SHMEM_BANK_SIZE - MMWAVE_MSSUSED_L3RAM_SIZE)

#define MMWAVE_L3RAM_DATA_SIZE (MMWAVE_MSSUSED_L3RAM_SIZE - MMWAVE_MSSUSED_L3RAM_CODESIZE)

MEMORY{

/*PAGE 0:*/

VECTORS (X) : o=0x00000000 l=0x00000100

PROG_RAM (RX) : o=0x00000100 l=0x0007FF00

DATA_RAM (RW) : o=0x08000000 l=0x00030000

L3_CODE_RAM (RW) : o=0x51000000 l=0x00000000+(MMWAVE_MSSUSED_L3RAM_CODESIZE)

L3_DATA_RAM (RW) : o=0x51000000+(MMWAVE_MSSUSED_L3RAM_CODESIZE) l=0x00000000+(MMWAVE_L3RAM_DATA_SIZE)

L3_DSS_RAM (R) : o=0x51000000+(MMWAVE_L3RAM_DATA_SIZE)+(MMWAVE_MSSUSED_L3RAM_CODESIZE) l=0x00000000+(MMWAVE_L3RAM_SIZE)

HWA_RAM (RW) : o=0x52030000 l=0x00010000

HS_RAM (RW) : o=0x52080000 l=0x8000

}

/*------------------------------------------------------------------------------*/

/* Section Configuration */

/*------------------------------------------------------------------------------*/

/* Name | Initialized | Notes */

/*------------------------------------------------------------------------------*/

/* .text | yes | executable code */

/* .bss | no | global variables */

/* .cinit | yes | tables which initialize global variables */

/* .data (EABI) | yes and no | initialized coming out of the assembler; */

/* | | changed to uninitialized by the linker */

/* .data (COFF ABI)| yes | initialized data */

/* .stack | no | system stack */

/* .heap | no | malloc heap */

/* .sysmem | no | malloc heap */

/* .const | yes | initialized global variables */

/* .switch | yes | jump tables for certain switch statements */

/* .init_array | yes | Table of C++ constructors called at startup */

/* .pinit | yes | Table of C++ constructors called at startup */

/* .cio | no | Buffer for stdio functions */

/*------------------------------------------------------------------------------*/

SECTIONS{

.intvecs : {} > VECTORS

.text : {} > PROG_RAM ALIGN(8)

.const : {} > PROG_RAM ALIGN(8)

.cinit : {} > PROG_RAM ALIGN(8)

.init_array : {} > PROG_RAM ALIGN(8)

.pinit : {} > PROG_RAM ALIGN(8)

.data : {} > DATA_RAM

.bss : {} > L3_CODE_RAM ALIGN(8)

.stack : {} > L3_CODE_RAM ALIGN(32)

.sysmem : {} > L3_CODE_RAM ALIGN(8)

}

/*------------------------------------------------------------------------------*/