Hi,

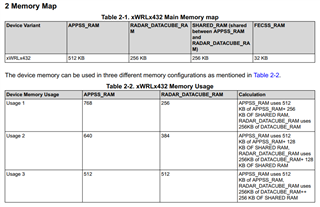

1. I found below info in TRM memory map section.

1. In our mmw demo, APP_HWA_RAM 0x60000000~0x6007FFFF(512k) is used. And didn't find code to configure HWA_PD_MEM_SHARE_REG. Is the device in Usage 3 in table 2-2 by default?

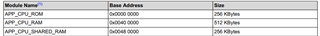

2. In TRM , I also found APP_CPU_SHARED_RAM info below. But in our demo, the address range 0x00480000~0x004BFFFF (256k) is not used. If user reconfigue HWA_PD_MEM_SHARE_REG to Usage 1, user can use address range 0x00480000~0x004BFFFF(APP_CPU_SHARED_RAM), right?

3. M4F accessing memory in APP_CPU_SHARED_RAM is faster than memory in APP_HWA_RAM, right?

Thanks,

Chris

In the demo, APP_HWA_RAM 0x60000000~0x6007FFFF(512k) is used.

I think there should be some HW overlap between APP_CPU_SHARED_RAM and APP_HWA_RAM. Is there any memory access speed difference for M4F to these two different address ranges?

2.