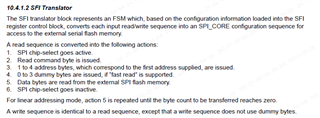

Hello Expert,

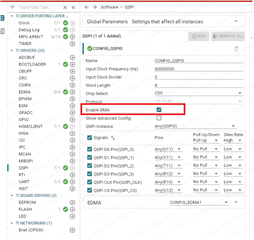

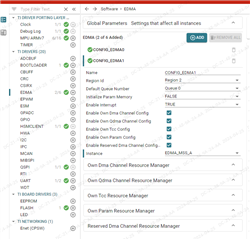

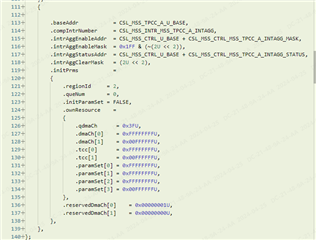

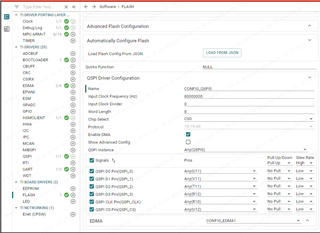

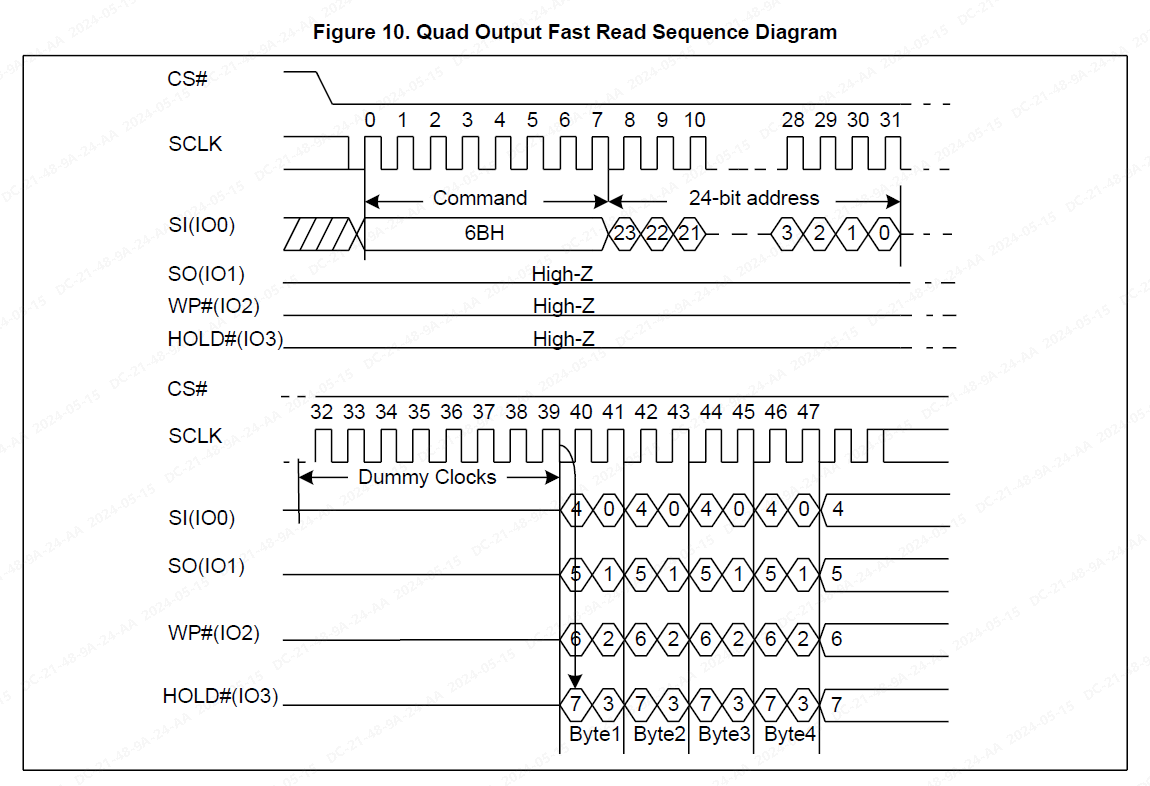

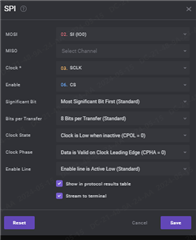

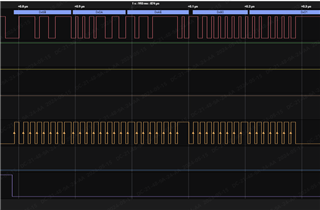

We set the QSPI input frequency to 80MHz and enabled DMA. Then, I observed the following clock signal waveform(read flash).

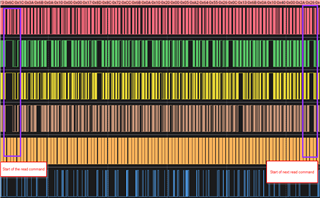

| CMD | Address | Data | Data | CMD | Address | Data | Data | ||||||

| 6BH | A23-A16 | A15-A8 | A7-A0 | dummy | 16bytes data | 16bytes data | 6BH | A23-A16 | A15-A8 | A7-A0 | dummy | 16bytes data | 16bytes data |

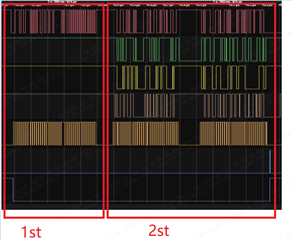

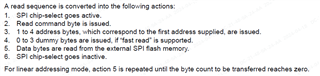

For every 32 bytes read, a command/address/dummy must be sent. Which is differenct with the discriptions of AWR294x Technical Reference Manual(action 5 is repeated until the byte count to be transferred reaches zero)

Is it correct? What does cause it? How to change our configuration to repeat action 5 until the byte count is zero?

Regards,

Wu Bin