Other Parts Discussed in Thread: SYSCONFIG, UNIFLASH

Hi,

I debugged the CSI2 mode by running it on the AWR 2844 ES1.0.

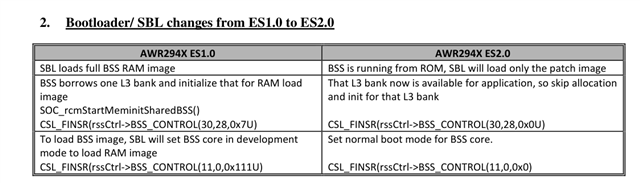

but when zhe AWR2944 ES1.0 to ES2.0 changes,zhe CSI2 mode cannot receive.

There are no changes related to CSI2 in the modification information from ES1.0 to ES2.0.

May I ask if there is any good solution?

Regards,

guilin.shi