Tool/software:

Hi Team,

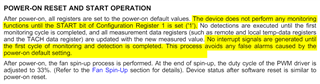

Based on below post that I2C communication is blocked within spin-up time(2 sec).

=> AMC6821-Q1: Cannot control when chip initialize early

=> We encounter the same issue and after 2 sec, the I2C write and read are all expected as what we set.

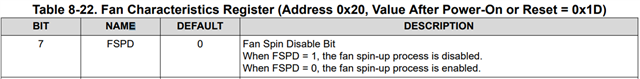

I notice the FSPD is "0" so once the VDD is powered, it will directly enter into spin-up cycle and no way to change that, is that correct?

After VDD is given, If we keep FSPD as "0", once the fan stops or an RPM is detected below the minimum speed, it will enter spin-up time again and lost the I2C communication for 2 sec again?

=> Assume we use the same STIMEx setting.

And why we have this 2s spin-up time design? What's the purpose of it?

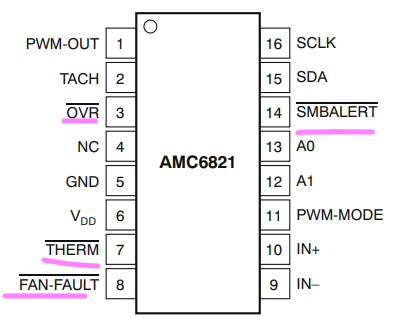

Customer use below 4 OD pin as indicator for SoC to judge whether we should start the I2C communication with AMC6821-Q1.

They said they notice these 4 pins might toggle so might not be a good indicator for SoC.

My question is whether the toggling phenomenon might happen randomly within above 2s spin-up time?

If this toggling phenomenon is due to certain fault, could we still check the 0x02(Device Status Registers) to know what happened within 2s spin-up time?

=> Maybe the WRITE function is blocked but READ function is available?

Looking forward to your reply.

Thank you.