Tool/software:

Hi team,

I want to check how to close the RDIF interface? Can I close the clock system for RDIF interface by setting adcLoging to ‘0’ to improve the EMI performance?

Regards,

Shawn

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

I want to check how to close the RDIF interface? Can I close the clock system for RDIF interface by setting adcLoging to ‘0’ to improve the EMI performance?

Regards,

Shawn

Hi Shawn,

One of our engineers will look into this and give you an answer within a day or two.

Hi Shawn,

You can try adclogging 2 which will switch off the RDIF interface

Regards,

Sreedeep

Hi Sreedeep,

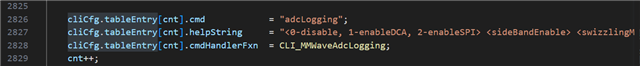

In our code, setting 2 means SPI and setting 0 is close this rdif. Can you help confirm this?

Regards,

Shawn

Hi Shawn,

Setting 2 will enable raw data capture through SPI, where RDIF will be closed. I will confirm if adclogging 0 will turn off the RDIF.

Regards,

Sreedeep

Hey Shawn,

By default, the RDIF clock - the MDLL clock derived from APLL clock - is disabled, so setting the adcLogging to 0 or 2 should keep the RDIF disabled. If adcLogging is set to 1, then the clock is enabled.

Regards,

Kristien