Tool/software:

Hi, support

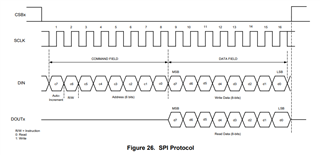

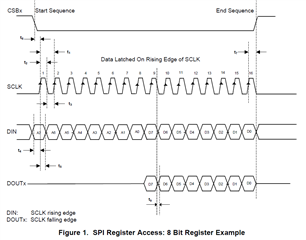

The text in the image states that the DIN: SCLK rising edge, DOUTx: SCLK falling edge. Is this referring to the setup time?

Could you please provide a more detailed explanation to help me understand this better? When does DOUT need to capture the data, thank you

Thank you.