Tool/software:

Hello,

we are encountering a limit when trying to maximize the total ADC sample time.

Our setting:

ADC Valid Start time: 7 us

# of Chirp loops: 512

# of samples per Chirp: 256

whenever we lower the velocity resolution (to make the chirp cycle time longer), to further lengthen the ADC sample time, we hit the rule of ADC sampling having to be > 2 MegaSamples per second. Which leads us to increase either Idle time or Excess ramp time, therefore shortening the ADC sample time. The highest we have been able to get is Total ADC sampling time (per single measurement) = 64ms. Do you see a way to increase the ADC sampling over 2Msps without the need of increasing Idle time/Excess ramp time which would give us longer ADC sample time when lowering the velocity resolution? Can the 2Msps requirement be omitted? How?

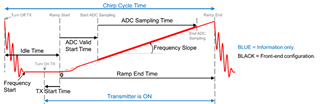

All time terms are used as per this image:

Thank you,

Pavel