Tool/software:

Hi L6432AOP Champ !

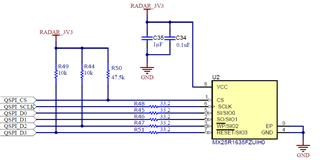

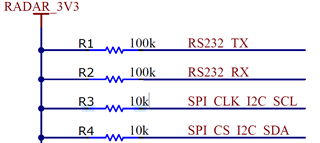

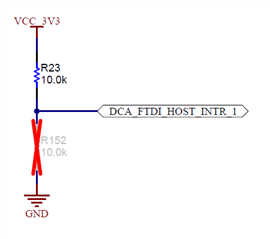

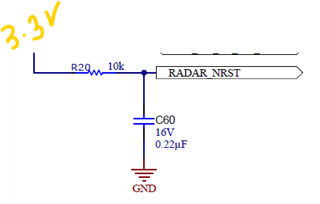

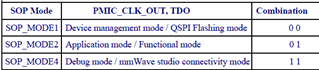

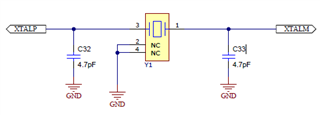

Can you please check the custom circuit design especially for bootmode, power rail, memory, connector which could be based on IWRL6432AOP?

My customer has done for Sensor area firstly, and used connector (8CON5) to connect to expandable area.

kspl2405_f_device_radar_6432_ws_rev01_20240724.pdf

Thanks, and Regards,

Jack