Tool/software:

In awr2944 tdm demo, cfar config occur error -2820. I search the error code, find it's hwa common config error. what shoule i do to solve the problem?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

In awr2944 tdm demo, cfar config occur error -2820. I search the error code, find it's hwa common config error. what shoule i do to solve the problem?

Hi Peng,

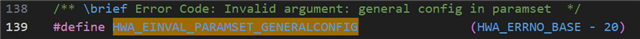

Error -2820 corresponds to HWA_EINVAL_PARAMSET_GENERALCONFIG. Can you please recheck the errorcode? Also use the latest SDK 4.6.1.2. Did you make any change in the SDK?

Regards,

Samhitha

Sorry, the error code is -2820, the screenshot is wrong. And sdk version is 4.6.0.1, i make some change in rangeDPU and dopplerDPU(mmw_resTDM.h)

/**

* @file mmw_res.h

*

* @brief

* Defines partitioning of hardware resources (HWA, EDMA etc) among the

* DPCs and other components in the millimeter wave demo.

*

* \par

* NOTE:

* (C) Copyright 2020-2021 Texas Instruments, Inc.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

#ifndef MMW_DEMO_RES_H

#define MMW_DEMO_RES_H

#ifdef __cplusplus

extern "C" {

#endif

#include <drivers/edma.h>

#include <ti/common/syscommon.h>

/* DPUs */

#include <dpu/rangeproc/rangeprochwa.h>

#include <dpu/dopplerproc/dopplerprochwa.h>

#include <dpu/cfarproc/cfarprochwa.h>

#include <dpu/aoaproc/aoaprochwa.h>

/*******************************************************************************

* Resources for Object Detection DPC, currently the only DPC and hwa/edma

* resource user in the demo.

*******************************************************************************/

/* EDMA instance used*/

/* HWA can only be accessed through DSS*/

#define EDMA_NUM_DMA_CHANNELS 64

#define DPC_OBJDET_EDMA_INSTANCE 0

#define DPC_OBJDET_EDMA_SHADOW_BASE EDMA_NUM_DMA_CHANNELS

#define DPC_OBJDET_HWA_WINDOW_RAM_OFFSET 0

#define DPC_OBJDEC_PARAMSET_START_IDX 0

/* Range DPU */

#define DPC_OBJDET_DPU_RANGEPROC_EDMA_INST_ID 0

#if defined(OBJ_DETECTION_TEST)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ0

#else

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_CH EDMA_DSS_TPCC_A_EVT_RSS_ADC_CAPTURE_COMPLETE

#endif

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 0)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_SIG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ1

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_SIG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 1)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAIN_SIG_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_PARAMSET_START_IDX DPC_OBJDEC_PARAMSET_START_IDX

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ2

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_SHADOW_0 (DPC_OBJDET_EDMA_SHADOW_BASE + 2)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_SHADOW_1 (DPC_OBJDET_EDMA_SHADOW_BASE + 3)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_SHADOW_2 (DPC_OBJDET_EDMA_SHADOW_BASE + 4)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_SHADOW_3 (DPC_OBJDET_EDMA_SHADOW_BASE + 50)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_SHADOW_4 (DPC_OBJDET_EDMA_SHADOW_BASE + 51)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_0_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ3

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_0_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 5)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_0_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_1_CH (EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ4)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_1_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 6)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_1_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_2_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ5

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_2_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 7)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_2_EVENT_QUE 0

/* Added for seqence 12341 usage*/

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_3_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ11

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_3_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 15)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_3_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_4_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ12

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_4_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 16)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PINGDATA_4_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ6

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_SHADOW_0 (DPC_OBJDET_EDMA_SHADOW_BASE + 8)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_SHADOW_1 (DPC_OBJDET_EDMA_SHADOW_BASE + 9)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_SHADOW_2 (DPC_OBJDET_EDMA_SHADOW_BASE + 10)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_SHADOW_3 (DPC_OBJDET_EDMA_SHADOW_BASE + 52)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_SHADOW_4 (DPC_OBJDET_EDMA_SHADOW_BASE + 53)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_0_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ7

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_0_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 11)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_0_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_1_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ8

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_1_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 12)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_1_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_2_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ9

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_2_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 13)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_2_EVENT_QUE 0

/* Added for seqence 12341 usage*/

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_3_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ13

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_3_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 17)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_3_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_4_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ14

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_4_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 18)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT2_PONGDATA_4_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ2

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 2)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ6

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 3)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ10

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 14)

#define DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_EVENT_QUE 0

/* Doppler DPU */

#define DPC_OBJDET_DPU_DOPPLERPROC_PARAMSET_START_IDX (DPC_OBJDET_DPU_RANGEPROC_PARAMSET_START_IDX + \

DPU_RANGEPROCHWA_NUM_HWA_PARAM_SETS)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_INST_ID DPC_OBJDET_EDMA_INSTANCE

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ15

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PING_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 54)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ16

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PONG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 55)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAIN_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ17

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PING_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 56)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ18

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PONG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 57)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMAOUT_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PING_SIG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ19

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PING_SIG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 58)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PING_SIG_EVENT_QUE 0

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PONG_SIG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ20

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PONG_SIG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 59)

#define DPC_OBJDET_DPU_DOPPLERPROC_EDMA_PONG_SIG_EVENT_QUE 0

/* Static Clutter DPU */

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMA_INST_ID DPC_OBJDET_EDMA_INSTANCE

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ21

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PING_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 21)

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ22

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PONG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 22)

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAIN_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PING_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ23

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PING_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 23)

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PONG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ24

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PONG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 24)

#define DPC_OBJDET_DPU_STATIC_CLUTTER_PROC_EDMAOUT_PONG_EVENT_QUE 0

/* CFAR DPU */

#define DPC_OBJDET_DPU_CFAR_PROC_PARAMSET_START_IDX (DPC_OBJDET_DPU_DOPPLERPROC_PARAMSET_START_IDX + \

DPU_DOPPLERPROCHWA_MAX_NUM_HWA_PARAMSET)

#define DPC_OBJDET_DPU_CFAR_PROC_EDMA_INST_ID DPC_OBJDET_EDMA_INSTANCE

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ31

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 60)

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_EVENT_QUE 0

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_SIG_CH EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ32

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_SIG_SHADOW (DPC_OBJDET_EDMA_SHADOW_BASE + 61)

#define DPC_OBJDET_DPU_CFAR_PROC_EDMAIN_SIG_EVENT_QUE 0

/* AOA DPU */

/* INTR_15 to INTR_18 are among those not presently used in the system,

* hence use it for general purpose, note an actual event coming on these

* will not falsely trigger the EDMA.

*/

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_INST_ID DPC_OBJDET_EDMA_INSTANCE

/* Event queues PING path */

#define DPC_OBJDET_DPU_AOA_PROC_EDMAIN_PING_EVENT_QUE 0

#define DPC_OBJDET_DPU_AOA_PROC_EDMAOUT_PING_EVENT_QUE 0

/* Event queues PONG path */

#define DPC_OBJDET_DPU_AOA_PROC_EDMAIN_PONG_EVENT_QUE 0

#define DPC_OBJDET_DPU_AOA_PROC_EDMAOUT_PONG_EVENT_QUE 0

/* EDMA physical channels tied to HWA output events */

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_HWA_OUTPUT_CH_0 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ23

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_HWA_OUTPUT_CH_1 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ24

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_HWA_OUTPUT_CH_3 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ29

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_HWA_OUTPUT_CH_4 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ30

/* EDMA general physical channels */

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_CH_0 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ25

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_CH_1 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ26

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_CH_2 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ27

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_CH_3 EDMA_DSS_TPCC_A_EVT_HWA_DMA_REQ28

#define DPC_OBJECT_DPU_AOA_PROC_EDMA_CH_4 EDMA_DSS_TPCC_A_EVT_CBUFF_DMA_REQ0

#define DPC_OBJECT_DPU_AOA_PROC_EDMA_CH_5 EDMA_DSS_TPCC_A_EVT_CBUFF_DMA_REQ1

/* EDMA Param sets */

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_0 (DPC_OBJDET_EDMA_SHADOW_BASE + 27)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_1 (DPC_OBJDET_EDMA_SHADOW_BASE + 28)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_2 (DPC_OBJDET_EDMA_SHADOW_BASE + 29)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_3 (DPC_OBJDET_EDMA_SHADOW_BASE + 30)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_4 (DPC_OBJDET_EDMA_SHADOW_BASE + 31)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_5 (DPC_OBJDET_EDMA_SHADOW_BASE + 32)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_6 (DPC_OBJDET_EDMA_SHADOW_BASE + 33)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_7 (DPC_OBJDET_EDMA_SHADOW_BASE + 34)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_8 (DPC_OBJDET_EDMA_SHADOW_BASE + 35)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_9 (DPC_OBJDET_EDMA_SHADOW_BASE + 36)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_10 (DPC_OBJDET_EDMA_SHADOW_BASE + 37)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_11 (DPC_OBJDET_EDMA_SHADOW_BASE + 38)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_12 (DPC_OBJDET_EDMA_SHADOW_BASE + 39)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_13 (DPC_OBJDET_EDMA_SHADOW_BASE + 40)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_14 (DPC_OBJDET_EDMA_SHADOW_BASE + 41)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_15 (DPC_OBJDET_EDMA_SHADOW_BASE + 42)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_16 (DPC_OBJDET_EDMA_SHADOW_BASE + 43)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_17 (DPC_OBJDET_EDMA_SHADOW_BASE + 44)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_18 (DPC_OBJDET_EDMA_SHADOW_BASE + 45)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_19 (DPC_OBJDET_EDMA_SHADOW_BASE + 46)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_20 (DPC_OBJDET_EDMA_SHADOW_BASE + 47)

#define DPC_OBJDET_DPU_AOA_PROC_EDMA_VIRT_CH_21 (DPC_OBJDET_EDMA_SHADOW_BASE + 48)

/*************************LVDS streaming EDMA resources*******************************/

/*EDMA instance used*/

#define MMW_LVDS_STREAM_EDMA_INSTANCE EDMA_DRV_INST_DSS_B

#define MMW_LVDS_STREAM_EDMA_SHADOW_BASE EDMA_NUM_DMA_CHANNELS

/* CBUFF EDMA trigger channels */

#define MMW_LVDS_STREAM_CBUFF_EDMA_CH_0 EDMA_DSS_TPCC_B_EVT_CBUFF_DMA_REQ0

#define MMW_LVDS_STREAM_CBUFF_EDMA_CH_1 EDMA_DSS_TPCC_B_EVT_CBUFF_DMA_REQ1

/* HW Session*/

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_0 EDMA_DSS_TPCC_B_EVT_FREE_0

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_1 EDMA_DSS_TPCC_B_EVT_RTIA_DMA_REQ0

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_2 EDMA_DSS_TPCC_B_EVT_RTIA_DMA_REQ1

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_3 EDMA_DSS_TPCC_B_EVT_RTIA_DMA_REQ2

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_4 EDMA_DSS_TPCC_B_EVT_RTIA_DMA_REQ3

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_5 EDMA_DSS_TPCC_B_EVT_RTIB_DMA_REQ0

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_6 EDMA_DSS_TPCC_B_EVT_RTIB_DMA_REQ1

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_7 EDMA_DSS_TPCC_B_EVT_RTIB_DMA_REQ2

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_8 EDMA_DSS_TPCC_B_EVT_RTIB_DMA_REQ3

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_9 EDMA_DSS_TPCC_B_EVT_WDT_DMA_REQ0

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_CH_10 EDMA_DSS_TPCC_B_EVT_WDT_DMA_REQ1

/* SW Session*/

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_CH_0 EDMA_DSS_TPCC_B_EVT_WDT_DMA_REQ2

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_CH_1 EDMA_DSS_TPCC_B_EVT_WDT_DMA_REQ3

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_CH_2 EDMA_DSS_TPCC_B_EVT_MCRC_DMA_REQ0

/*shadow*/

/*shadow CBUFF trigger channels*/

#define MMW_LVDS_STREAM_CBUFF_EDMA_SHADOW_CH_0 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 0U)

#define MMW_LVDS_STREAM_CBUFF_EDMA_SHADOW_CH_1 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 1U)

/* HW Session*/

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_0 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 2U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_1 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 3U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_2 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 4U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_3 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 5U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_4 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 6U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_5 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 7U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_6 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 8U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_7 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 9U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_8 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 10U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_9 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 11U)

#define MMW_LVDS_STREAM_HW_SESSION_EDMA_SHADOW_CH_10 (MMW_LVDS_STREAM_EDMA_SHADOW_BASE + 12U)

/* SW Session*/

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_SHADOW_CH_0 (EDMA_NUM_DMA_CHANNELS + 13U)

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_SHADOW_CH_1 (EDMA_NUM_DMA_CHANNELS + 14U)

#define MMW_LVDS_STREAM_SW_SESSION_EDMA_SHADOW_CH_2 (EDMA_NUM_DMA_CHANNELS + 15U)

/*************************LVDS streaming EDMA resources END*******************************/

#ifdef __cplusplus

}

#endif

#endif /* MMW_DEMO_RES_H */

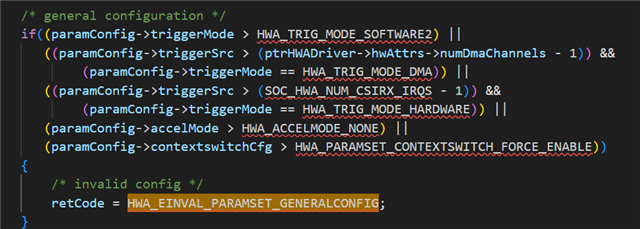

I find the reason is triggerSrc. triggerSrc=34, it occur error, if triggerSrc=0, it work ok.

Another question: If range DPU use paramset index is: 0-5, doppler DPU used paramset index is :6-33, so cfar dpu used paramset start index can begin 34?

Hi Peng,

Yes, you can use the paramsets which are not in use. So, RangeCFAR paramset start index can be 34.

Regards,

Samhitha

when paramset start index set to 34, it occur error, error code is -2820.

The current situation is:

range DPU: paramset index: 0-5, total 6

doppler DPU: paramset index: 6-33, total 28

-----------------------------

cfar paramset start index set: 5, 6, 10, 20 etc, error code is -2808;

cfar paramset start index set: 33, 34, 40 etc, error code is -2820;

Hi Peng,

I will check and let you know by early next week.

Regards,

Samhitha

Hi Peng,

In the current TDM demo, we are reusing the dopplerproc paramsets to configure the Cfar paramsets. If cfar paramsets configured after the end dopplerproc paramsets, I don't see any issue. Seems like there is something wrong with the paramsets that you have added. Please check it at your end as the issue cannot be reproduced at our side.

Regards,

Samhitha