Other Parts Discussed in Thread: , INA229

Tool/software:

Hi,

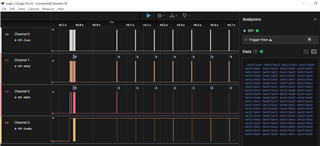

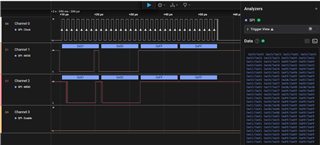

I am using an STM32F469BIT7 microcontroller to communicate with the TMP126 chip via the SPI1 bus. However, I am encountering an issue where the chip does not respond to commands such as reading the Config Register, Temp Result Register, THIGH_Limit, and TLOW_Limit register values.

As per my understanding, the TMP126 requires 16-bit data transfers. Therefore, I have configured my SPI bus to communicate using a 16-bit data frame.

According to the TMP126 datasheet, "Data is clocked out on the falling edge of the serial clock (SCLK), while data is clocked in on the rising edge of SCLK." This suggests that the SPI mode should be 1, where CPOL = 0 and CPHA = 1.

Here are the SPI settings I have configured:

- SPI Speed: 5.625 MHz

- CPOL: 0

- CPHA: 1

- Data Size: 16 bits

The SPI bus is configured as follows: