Tool/software:

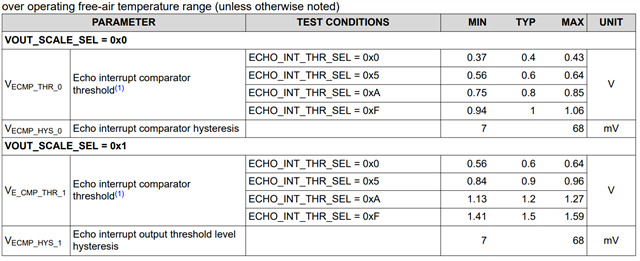

1. The datasheet for the TUSS4470 indicates that the output peak to peak noise varies from 75mV to 300mV with a 5V supply.

What would be the typical peak to peak noise? Does it apply to all the dynamic range or does it vary along the dynamic range?

Does the "Receiver path dynamic range" specification take into account the peak to peak noise?

2. The block diagram seems to indicate that the output driver circuit is independent of the analog receiver.

Is there any specific constraint to be aware of if the transducer is driven by an external circuit and only the analog receiver is used?

3. EMI susceptibility is a concern.

It looks like the receive input circuit uses a differential stage. With the calculations providing different component values for Cinp and Cinn,

does it increase EMI susceptibility? What would be the requirements of Cinp, Cinn, Rinp for best EMI susceptibility immunity?

Was there any test done on EMI susceptibility for the device? If so what are the results?