Other Parts Discussed in Thread: AWR2243, , DCA1000EVM

Tool/software:

Hello experts,

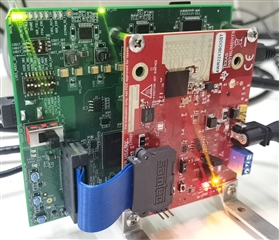

I am testing awr2243. the hardware is AWR2243Boost and DCA1000EVM.the config file of 2243 is attached.

the adc output is about +/- 200 with tx is disabled and rx gain is 48.

is the value normal in your experence? how can i decrease the value to lower than +/- 20 with the same conditions?

Best regards,

# #For detailed view of mmWave Radar configuration structure #please refer #ti\control\mmwavelink\docs\doxygen\html\index.html # # #Global configuration #Firmware download enable/disable; 1 - Enable; 0 - Disable #mmWaveLink logging enable/disable; 1 - Enable; 0 - Disable #Transport mode; 1 - I2C; 0 - SPI #Flash connected enable/disable; 1 - Enable; 0 - Disable # EnableFwDownload=1; EnableMmwlLogging=0; TransferMode=0; IsFlashConnected=1; #END # #power on master arguments, please modify if needed. #rlClientCbs_t: crcType 0:16Bit/1:32Bit/2:64Bit, # ackTimeout: This timeout value can vary on different PC, user needs to recalibrate # this value based on the system where this application runs. Ideally ackTimeout # should be in range of ~5mSec # crcType=1; ackTimeout=50000; #END # #channel config parameters, please modify if needed. #rlChanCfg_t # channelTx=1; channelRx=3; cascading=0; #END # #ADC out config parameters, please modify if needed. #rlAdcOutCfg_t # adcBits=2; adcFormat=1; #END # #DATA format config parameters, please modify if needed. #rlDevDataFmtCfg_t # rxChanEn=3; adcBitsD=2; adcFmt=1; iqSwapSel=0; chInterleave=0; #END # #Low power config Paramters, please modify if needed. #rlLowPowerModeCfg_t # anaCfg=0; lpAdcMode=0; #END # #Data Path config parameters, please modify if needed #rlDevDataPathCfg_t # intfSel=1; transferFmtPkt0=1; transferFmtPkt1=0; cqConfig=2; cq0TransSize=64; cq1TransSize=64; cq2TransSize=64; #END # #LVDS clock config parameters, please modify if needed #rlDevDataPathClkCfg_t # laneClk=1; dataRate=1; #END # #SET HSI clock parameters, please modify if needed. #rlDevHsiClk_t # hsiClk=9 #END # #LANE config parameters, please modify if needed. #rlDevLaneEnable_t # laneEn=3; #END # #LVDS Lane Config parameters, please modify if needed. #rlDevLvdsLaneCfg_t # laneFmtMap=0; laneParamCfg=1; #END # #Programmable Filter config parameters, please modify if needed. #rlRfProgFiltConf_t # profileId=0; coeffStartIdx=0; progFiltLen=14; progFiltFreqShift=100; #END # #Profile config parameters, please modify if needed. #rlProfileCfg_t # profileId=0; pfVcoSelect=2; startFreqConst=1471594320; idleTimeConst=200; adcStartTimeConst=300; rampEndTime=4500; txOutPowerBackoffCode=0; txPhaseShifter=0; freqSlopeConst=52; txStartTime=0; numAdcSamples=800; digOutSampleRate=22500; hpfCornerFreq1=0; hpfCornerFreq2=0; rxGain=176;#176(36db+48db) #END # #Chirp Configuration parameters, please modify if needed. #rlChirpCfg_t # chirpStartIdx=0; chirpEndIdx=0; profileIdCPCFG=0; startFreqVar=0; freqSlopeVar=0; idleTimeVar=0; adcStartTimeVar=0; txEnable=0; #END # #Frame configuration parameters, please modify if needed. #rlFrameCfg_t # chirpStartIdxFCF=0; chirpEndIdxFCF=0; frameCount=16; loopCount=160; periodicity=4000000; triggerDelay=0; numAdcSamples=1600; triggerSelect=1; #END