Other Parts Discussed in Thread: IWRL6432

Tool/software:

Hi TI Experts,

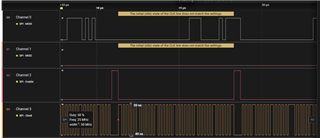

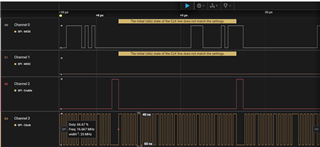

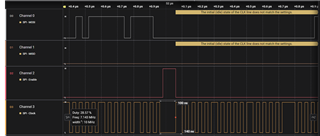

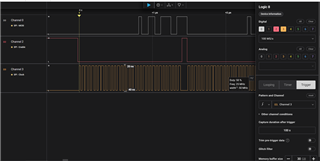

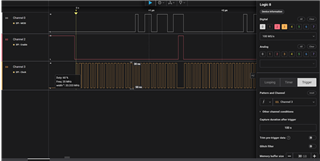

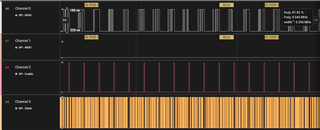

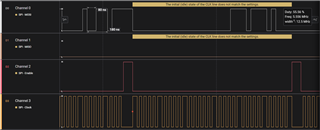

I have been evaluating the IWRL6432 mm Wave sensor for one of our applications, I wanted to obtain raw ADC data from the sensor using SPI through a Salae Logic 8 Analyzer. I followed the instructions as provided by your guide in the following link SPI Data Capture Users Guide. My Logic Analyzer could obtain a max sample speed of 50MS/s, The settings for my logic analyzer for obtaining SPI data are shown in below figures. I'm getting binary data but in some areas of the MOSI waveform, it gives an error showing "The initial (idle) state of the CLK line does not match the setting" at several areas of the entire waveform, although data comes during rest of times, I'm uncertain of the reliability of the data.

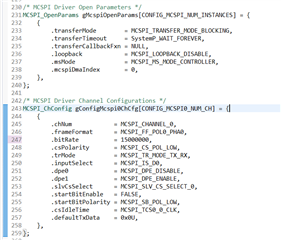

- I used the source code provided in the radar toolbox with path ti\radar_toolbox_2_20_00_05\source\ti\examples\Fundamentals\xWRL6432_Raw_Data_Over_SPI and made the changes by defining the macros SPI_DATA_STREAMING to 1 and SPI_DATA_STREAMING_MODE to 2 for logic analyzer.

- I flashed the program to the radar using the visualizer tool.

- I pasted the configuration in the path ti\radar_toolbox_2_20_00_05\source\ti\examples\Fundamentals\xWRL6432_Raw_Data_Over_SPI\chirp_configs\xwrl6432boost named MotionDetect_SPI_Data_Capture_LA.cfg to tera term after connecting to the XDS110 UART COM port.

- I started capture in logic analyzer and issued sensorStart 0 0 0 0 command after sending all previous configurations to the iwrl6432.

- I receive the waveforms as follows

Why this error shown in above image occurs?

- Are these steps that I followed for obtaining SPI data correct or is there anything I'm missing here?

- Is the cause for this issue due to the fact that 50MS/s sample speed of my logic analyzer too low for this if so, are there any solutions such as lowering the SPI bitrate as such?

- Is this error occurring due to some other issue maybe configuration file or source code.

Your support in this is much appreciated.

Thanks