Tool/software:

Hi team,

This is Lina covering Radar in Korea.

My customer asked me some questions about the antenna on the HW check list.

https://www.ti.com/lit/zip/swrr197

![]()

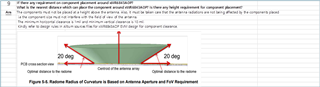

In that document, There is request for a 20 degree clearance interval from left to right of the IC.

- Should the criteria of 20 degrees be based on the IC Package edge?

- If you look at the AOP Data Sheet, the beam angle is 120 degrees x 120 degrees

I'm curious about the reason why you guide the clearance angle to 20 degrees. If I adjust it to 40 degrees, will there be a significant difference in antenna performance?

Regards,

Lina Kim