Tool/software:

Hi all,

Hopefully someone has encountered this issue and knows the root cause. But going solely from the datasheet, I don't understand why this is happening.

I have the OPT4060 configured for latching interrupts with a short ~2 ms conversion time. My expectation is that whenever FLAG_H or FLAG_L is set, the interrupt goes active, I read the status register, the interrupt goes away, and I see which flag popped to determine if a light turned on or off.

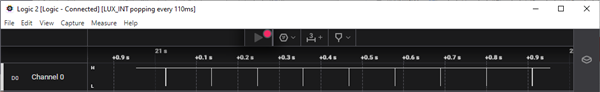

Unfortunately, what I'm seeing is this:

Those interrupts are popping every ~110.4 ms or so. "A-ha", you say, "clearly what you've done is set INT_CFG to give you an interrupt after every conversion is complete!" Nope. My configuration registers are set to 0x08BA and 0x8031 respectively. Breaking them out:

config_1 = 0x08ba (0000 1000 1011 1010) QWAKE = 0 RANGE = 0010b = 2 (9000 lux) CONV_TIME = 0010b = 2 (1.8 ms) OP_MODE = 11b = 3 (continuous) LATCH = 1 (latched, not transparent) INT_POL = 0 (active low) FAULT_COUNT = 10b = 2 (4 faults) config_2 = 0x8031 (1000 0000 0011 0001) BIT_15 = 1 THRESHOLD_CH_SEL = 01b = 1 (CH1 grn) INT_DIR = 1 (output) INT_CFG = 00b = 0 (SMBUS/latch) I2C_BURST = 1 (enable)

When these rogue interrupts pop, my code immediately disables my internal interrupt and gives a semaphore. My foreground code then wakes up and reads STATUS (reg 0xC), which clears the interrupt. Problem is, STATUS is 0... there's no conversion ready, no flags, no overload. So my code wakes up 9 times a second just to service spurious interrupts. INT_CFG is 0, not 1 or 3, so it shouldn't be popping when a new conversion is ready. And LATCH is 1, meaning that FLAG_H and FLAG_L should trigger INT* and reading 0xC clears INT*.

Any idea what I might be doing wrong here? Why is an interrupt being triggered every 110 ms with these configuration settings under steady office light?

Dana M.