Tool/software:

Hi team,

Does TMAG3001 have a special way to release SDA when the SDA stacked at low accidentaly?

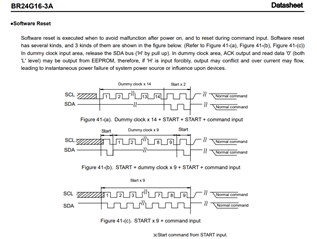

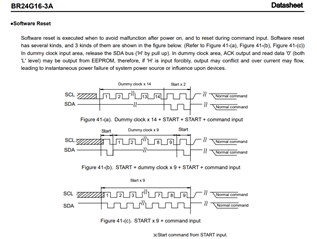

Following image is a snapshot from Rohm's EEPROM datasheet. It has some software reset.

Regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

Does TMAG3001 have a special way to release SDA when the SDA stacked at low accidentaly?

Following image is a snapshot from Rohm's EEPROM datasheet. It has some software reset.

Regards,

Hi Atsushi,

Thank you for posting to the Sensors forum!

The TMAG3001 does not have a software reset function as described in the snippet from the datasheet shown. But the TMAG3001 doesn't have an EEPROM or a cancel command function like the device mentioned in the datasheet, so I do not believe that this functionality is needed for the TMAG3001.

Best,

~Alicia

If SDA is stuck low, it can (usually) be cleared by sending (8+1) clock pulses on SCL. This is described in I2C Spec (UM10204 rev 7) Section 3.1.16.

This condition usually occurs when a master-receiver (for whatever reason) stops sending clocks in mid-byte. The clock pulses allow the slave to complete the byte, then the following clock looks like a NACK. I recommend sending all 9 pulses, since the master can't really detect if the bus clears earlier.

Alicia-san, Bruce-san,

Thank you for your advice.I have several questions.

1. When the TMAG3001 pulls SDA low, does SDA always go high after 9 clocks (even if the byte completes before 9 clocks and a NACK alredy occurs)?

2. If the answer above is Yes, do we need a stop condition after 9 clocks?

3. If the answer above is No, what should we do to clear the stack?

4. When the TMAG3001 receives a start condition, does the TMAG3001 discard the previous communication and start a new one?

If the fourth question is Yes, it means that the software reset example described in the Datasheet of Rohm's EEPROM is applicable. At the bottom of the three examples of software resets, 9 start condition are created by inputting the clock nine times. This is to clear the SDA stack by turning SDA high somewhere within 9 times, establishing the start condition, discarding the previous communication, and starting a new communication. Can we do the same with the TMAG3001?

Best Regards,

1) The 9-clocks trick usually works, but isn't guaranteed; it's possible the slave is permanently stuck (for its own reasons). If it doesn't succeed you need to use Plan B [Sec 3.1.16 doesn't call it that] which is to reset/power-cycle the slave; this is also the (only) solution if it's holding SCL low. SDA may go high before the slave has really released the bus -- it may just be shifting out a 1 bit.

2) I usually include a Stop, since I'm wiggling the GPIOs anyway. The NACK is supposed to be the signal for the slave to abandon the transaction.

3) You didn't mention what your host (master) is, so I can't say how much state you need to unwind. The master may already think the transaction is over.

4) I haven't worked with the TMAG3001 specifically, but in general a Start signifies the beginning of a new transaction. If it's interpreted as a Restart, some state may be retained. (Reading the TMAG3001 datasheet, it's not clear to me how "sticky" the Register Pointer is.)

In the Rohm excerpt I take "Software Reset" to mean something stronger than an I2C Bus Clear (which is what I'm describing).

I don't know if (e.g.) the TMAG3001 interprets 14x clocks followed by 2x Starts in any special way. [Alicia suggests it doesn't.] Items (b)/(c) are not applicable, since with the slave holding SDA low the master can't issue a Start (or a Stop).

[Edit: Small clarification.]