Other Parts Discussed in Thread: DCA1000EVM, , MMWAVE-SDK

Tool/software:

Hi TI team,

I am using IWR6843ISK + DCA1000EVM and using mmwave studio to configure every thin.

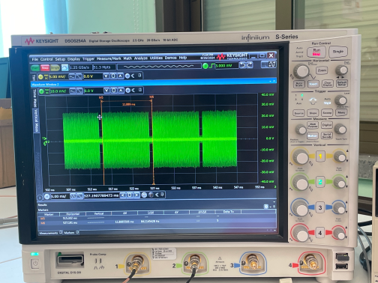

I faced a problem with the clock drift, I used the receiver as well as the down-converter and connected it to the oscilloscope, but seems like the frame periodicity is not exactly the same as the periodicity I set. Also, the frame time drift is also changing with time, for example, the setting is 10ms, but actually, it is 10.00055ms from the oscilloscope, and later it becomes 10.00065ms. And the change of the frame periodicity doesn't change linearly with time.

So my questions are:

1. Is there any calibration that can help? (I know that by default APLL and VCO Synth run time calibration happens every 1 second) But is there any way to make this calibration for every frame?

2. Is there a model to describe such a clock drift?

3. Are there any workarounds?

Here is my chirp and frame setting, I am not sure if the parameters I am using influence the frame periodicity I mentioned. Interframe time I set is 788 us.

"rlProfiles": [

{

"rlProfileCfg_t": {

"profileId": 0,

"pfVcoSelect": "0x2",

"pfCalLutUpdate": "0x0",

"startFreqConst_GHz": 60.0,

"idleTimeConst_usec": 5.0,

"adcStartTimeConst_usec": 3.0,

"rampEndTime_usec": 20.0,

"txOutPowerBackoffCode": "0x0",

"txPhaseShifter": "0x0",

"freqSlopeConst_MHz_usec": 50.0,

"txStartTime_usec": 0.0,

"numAdcSamples": 212,

"digOutSampleRate": 12500,

"hpfCornerFreq1": 0,

"hpfCornerFreq2": 0,

"rxGain_dB": "0x1E"

}

}

],

"rlChirps": [

{

"rlChirpCfg_t": {

"chirpStartIdx": 0,

"chirpEndIdx": 0,

"profileId": 0,

"startFreqVar_MHz": 0.0,

"freqSlopeVar_KHz_usec": 0.0,

"idleTimeVar_usec": 0.0,

"adcStartTimeVar_usec": 0.0,

"txEnable": "0x1"

}

}}

"rlFrameCfg_t": {

"chirpEndIdx": 1,

"chirpStartIdx": 0,

"numLoops": 222,

"numFrames": 0,

"framePeriodicity_msec": 11.888,

"triggerSelect": 1,

"numDummyChirpsAtEnd": 0,

"frameTriggerDelay": 0.0

}

Best,

Bei