Tool/software:

Hello, TI team,

I have a question about hardware triggered mode.

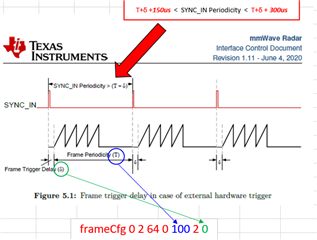

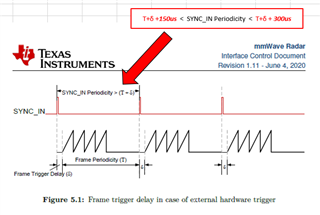

The document "mmWave Radar Interface Control Document Revision 1.11" states that the periodicity of pulse is configured to occur 150us after the completion of previous frame, and it is recommended that the time delta between end of previous frame and rising edge of HW pulse be < 300us.

I believe that if the above is represented in a diagram, it would look like the figure below (T+δ +150us < SYNC_IN Periodicity < T+δ + 300us)

Is my understanding correct?

Regards,

Kei