Tool/software:

*Re-upload to public E2E as the person in charge commented

.

.

Hi team,

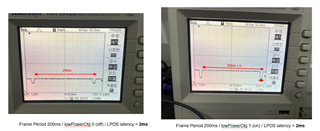

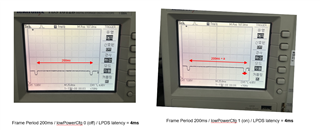

Regarding LPDS mode (lowPowercfg 1 or 2), there is an issue.

When customer set lowPowercfg 1 or 2, both case face frame time delay issue.

No fixed time delay, there is a different time delay for each Frame cycle setting.

The code used basic examples with no modifications. They found that it happened in both examples.

.

.

I received an answer from Kristien to adjust the LPDS latency value.

So, I increased the LPDS latency value and tested it. My additional questions are below.

- ‘xWRL6432 Power Consumption.pdf’ contains LPDS latency, with a typical time of 2ms. Can you tell me how the value of 2ms came out?

- If what I understand is correct, Remain frame time cannot be changed and sleep time is expected to be reduced when the LPDS latency value is adjusted to more than 2ms, so does that not affect power consumption?

- If you check the attached test results, you can see an error when set above a certain value.

I think it is inefficient to test all values so that frame delay does not occur. Is there a guide to how much LPDS latency should be set if the frame period is x ms? The method of putting it one by one and checking it through the oscilloscope is less reliable.

Regards,

Lina