Tool/software:

The project requires implementing the functionality to enable the PMIC watchdog in the application (app) and disable it in the bootloader (boot).

For OTA, the system needs to transition from the app to the boot for the upgrade process.

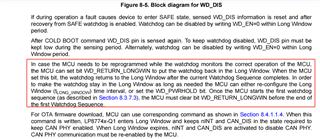

Since the PMIC watchdog is enabled in the app, it cannot be directly disabled after transitioning to the boot.

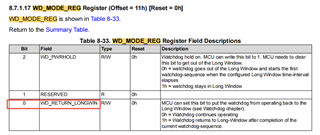

Currently, before transitioning from the app to the boot, I first write to bit 0 (WD_RETURN_LONGWIN) of the PMIC register WD_MODE_REG via mibspi.

Then, I wait for 500 milliseconds and perform a warm reset to jump to the boot.

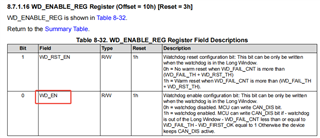

In the boot, I disable the watchdog by writing 0 to the PMIC register WD_ENABLE_REG.

My issue is that there is a probability of failure in the PMIC watchdog configuration during this process,

which prevents the watchdog from being properly disabled in the boot.

Could you please help identify the root cause of this problem and suggest how it should be resolved?