Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello team,

.

My customer set as below but still L3 memory doesn't look retained. Can we provide guidance how to retain L3 memory? What are they missing?

.

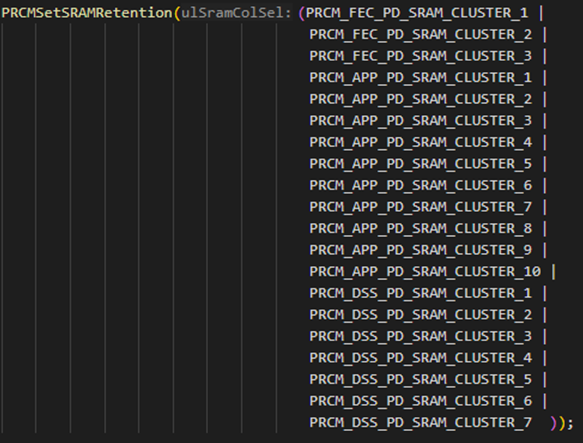

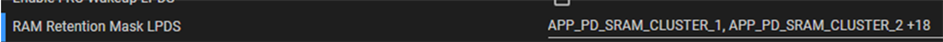

Sysconfig

.

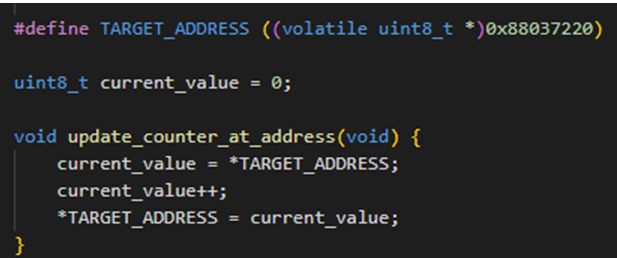

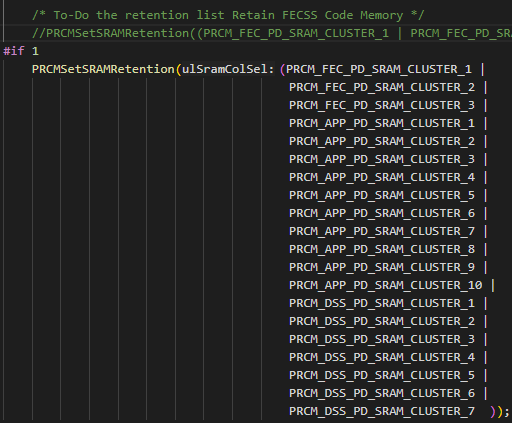

in DPC_Execute

.

Regards,

Victor Park