Other Parts Discussed in Thread: AWR2544

Tool/software:

Hi,

I am developing CSI2 driver on awr2544 to enable streaming raw ADC data via CSI2-TX. From the other end, I'm using CSI2-RX of TMDS273x to receive that raw ADC data and further process on AM273x SoC (FFT, CFAR...). I have it implemented based on cbuff lvds module.

However, I am little confusing of packetization configuration on some CSI2 registers. Here are the CSI2 registers I may need your help:

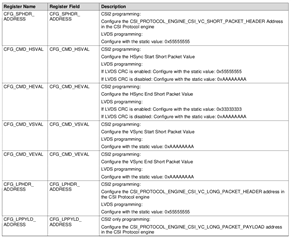

- CFG_SPHDR_ADDRESS - Configure the CSI_PROTOCOL_ENGINE_CSI_VC_SHORT_PACKET_HEADER Address in the CSI Protocol engine

- CFG_LPHDR_ADDRESS - Configure the CSI_PROTOCOL_ENGINE_CSI_VC_LONG_PACKET_HEADER address in the CSI Protocol engine

- CFG_LPPYLD_ADDRESS - Configure the CSI_PROTOCOL_ENGINE_CSI_VC_LONG_PACKET_PAYLOAD address in the CSI Protocol engine

- CFG_CMD_HSVAL - Configure the HSync Start Short Packet Value

- CFG_CMD_HEVAL - Configure the HSync End Short Packet Value

- CFG_CMD_VSVAL - Configure the VSync Start Short Packet Value

- CFG_CMD_VEVAL - Configure the VSync End Short Packet Value

I have referred to MIPI CSI2 v1.3 specification, however I couldn't find much information about the value should be written to above registers.

Can you please recommend the values for those registers to get CSI2-TX engine on awr2544 functioning with CSI2-RX engine on AM273x SoC?

Thanks!

QHLam