Tool/software:

Hello,

I'm working on a board that uses the IWRL6432AOP radar chip, but I'm a bit unsure about the layout.

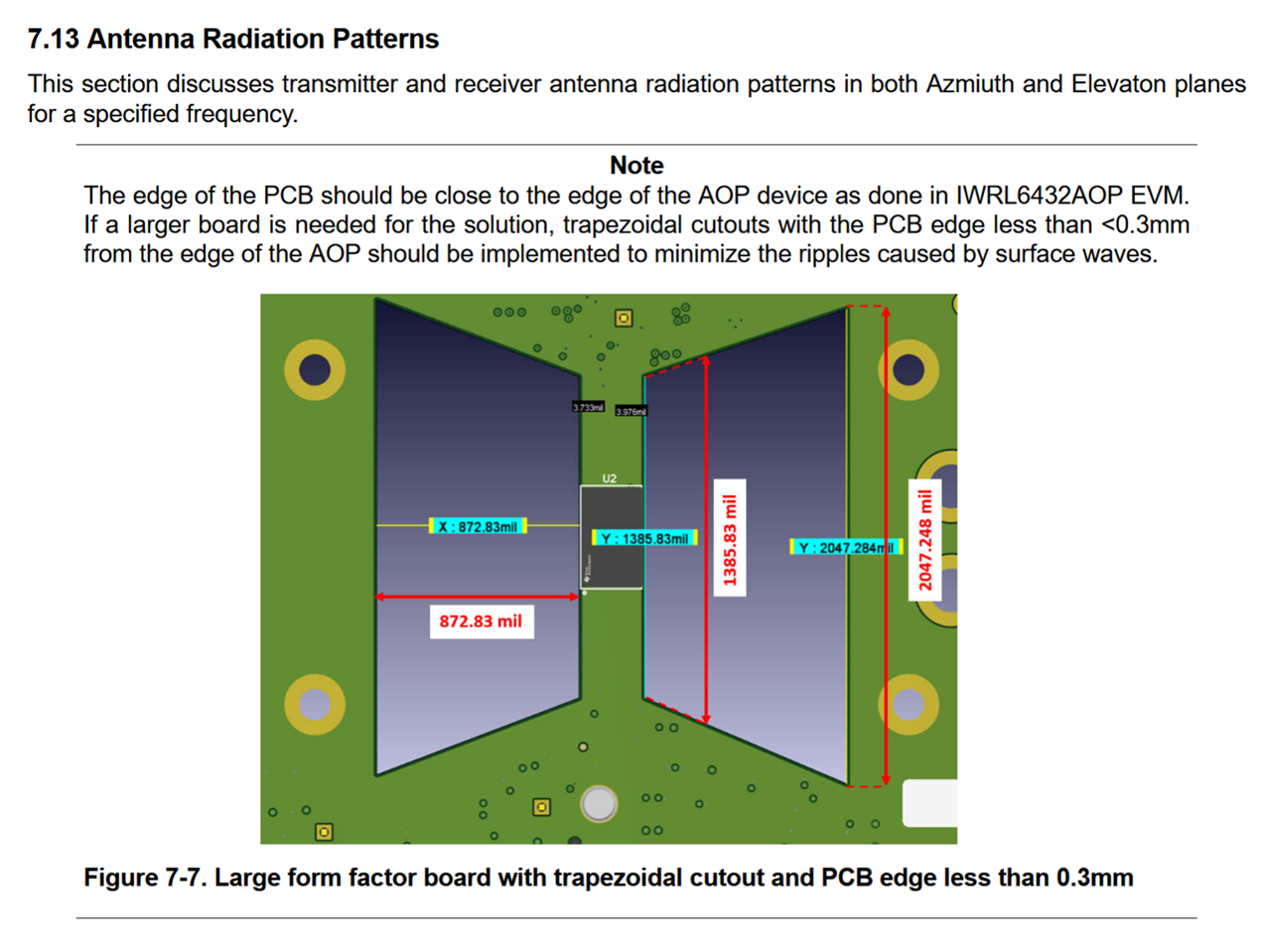

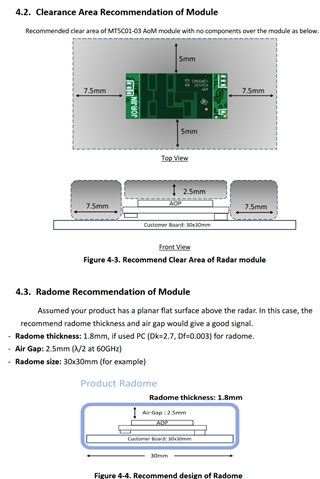

The datasheet recommends this but that makes the PCB really big and cumbersome. The IWRL6432AOPEVM don't really adhere to these guidelines either and there is another module that only needs a spacing of around 5mm on all sides so I'm not entirely sure what to do now. Ideally I would place the chip in the middle of the PCB but I'm not sure if this interferes with the radar waves too much. Thanks for the help!