Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Dear TI experts,

I have ever post a question about flash mmap access last year: https://e2e.ti.com/support/sensors-group/sensors/f/sensors-forum/1206158/iwrl6432-qspiflash-mmap

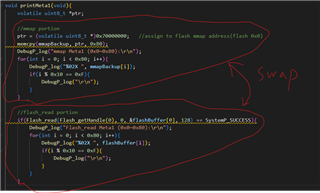

memory adreess 0x70000000 is able to be read as flash 0x0 offset, while first time power on,

but I am encountering the reading from mmap address but data corrupted problem after go through Low power deep sleep(LPDS).

How to duplicate: (use "mmwave_l_sdk 5.5.3.0" )

1. Import "examples\drivers\power\power_modes"

2. in sysconfig, add "FLASH" to board drivers, keep default config for it.

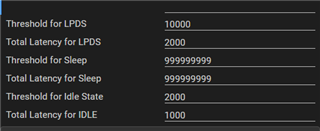

3. in sysconfig, change "Power" setting, make it be suitable in real world... .

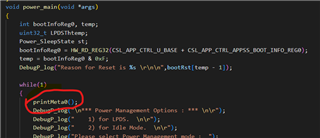

4. Open the "power_modes,c", add a test function: "printMeta0", it will print front 128 bytes part of current appimage in Meta1 location.

and make it be execute inside of the while loop

5. build image and upload to boost EVM board, let's check the result.

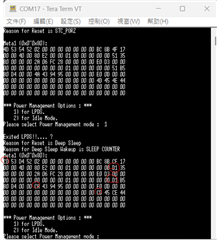

you can see the power on, the output is correct and the same with built appimage.

but if press '1' to go with LPDS, the output is all "zero" values, repeat again will get corrupted output...

Could you please investigate this problem? and how can I read correct data from mmap address after LPDS....