Other Parts Discussed in Thread: AWR2243

Tool/software:

Hello Expert,

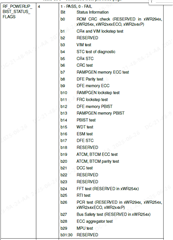

We found discrepancies in the description of the radarSS bootup status bit definition between the documentation(mmWave-Radar-Interface-Control.pdf) and the code comments in rl_sensor.h (in the rlRfBootStatusCfg structure). Which one is correct?

The sdk version is mmwave_mcuplus_sdk_04_07_01_01.

/**

* @brief radarSS bootup status

Bit definition [1: pass, 0: fail]

0 image CRC validation (RESERVED in xWR294x/xWR254x/xWR2x4xP)

1 CPU and VIM self-test status

2 Reserved

3 VIM test

4 STC self-test

5 CR4 STC

6 CRC test

7 Pampgen ECC

8 Reserved

9 DFE ECC

10 Rampgen Lockstep

11 FRC lockstep

12 DFE PBIST

13 Rampgen lockstep

14 PBIST test

15 WDT test

16 ESM test

17 DFE STC

18 FRC test

19 TCM ECC

20 TCM parity

21 DCC test (Supported only on

AWR2243/xWR6243/xWR294x/xWR254x/xWR2x4xP device)

22 SOCC test

23 GPADC test

24 FFT test (RESERVED in xWR254x/xWR2x4xP)

25 RTI test

26 PCR test (RESERVED in xWR294x/xWR254x/xWR2x4xP)

27 Bus safety test (RESERVED in xWR254x/xWR2x4xP)

28 ECC aggregator test

29 MPU test

31:30 reserved

*/

rlUInt32_t bssSysStatus;

Regards,

Wu Bin