Tool/software:

Hi:

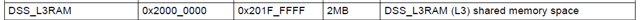

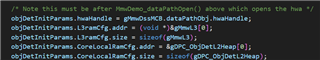

I'm now developing based on OOB demo of 1843boost. Currently I've modify the code so the whole DPC chain is running purely on DSP. I would like to know how the whole DPC memory is allocated. I checked the manual and it seems like the memory 0x5100_0000~0x51FF_FFFF is allocated as L3RAM for DDS as a shared memory. Is this memory address fixed somehow or it is configured during the DPC_ObjDetDSP_preStartConfig? I went through the code and I'm sure there are memory allocation operation there but the allocated address start from 0x0080_xxxx etc. How does this memory allocation operation related to the 0x5100_0000?

Regards