Tool/software:

Hi,

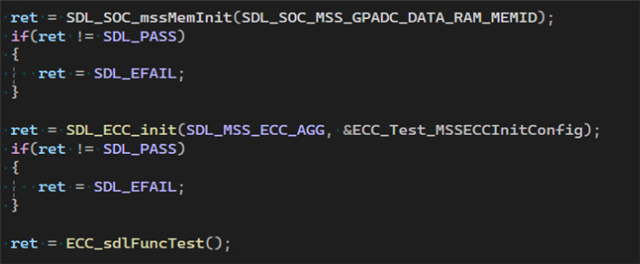

I'm trying to implement ECC Memory test for the MSS regions in ECC_AGG_MSS.

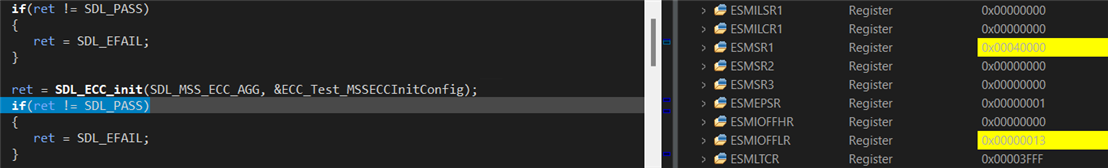

Sometimes, as soon as SDL_ECC_Init() is called, ESM interrupt flag for this ECC Aggregator is set.

Once this happens, even if I clear the flag in ESMSR1, I don't see the interrupt when I inject a bit error.

after few power cycles, this doesn't happen. and I get interrupt pending status in ESMSR1 when a bit error is injected.

Any input on why I'm seeing this every few power cycles?

Note: all the error status flags are cleared during ESM initialization stage. and whenever a status flag is set, it is cleared after read.

So, if an Error status flag is set in one cycle, it should not affect the next one.