Tool/software:

I am seeking clarification on the time available for transferring chirps over CSI

From SWRA555A - AWR1xxx and AWR22xx Data Path

The AWR2243 has a ping-pong buffer for storing chirps, allowing a chirp to be read into the ping buffer while the pong buffer is transferred over CSI/LVDS.

The key DFE events that trigger the state machine are the “Frame Start” and “Chirp(s) Available” events.

The “Chirp(s) Available” event is generated during every ping-pong switch of the ADC buffer. On every

“Chirp(s) Available” event, the CBUFF kicks the eDMA configured eDMA channel for the transfer and the

flow control mechanism ensures the complete transfer of the data over the HSI interface. - Section 4.1.1 State Machine

So whenever the ADC sampling for a chirp ends, a Chirp(s) Available event is generated and the buffer switches from being read into, to being transferred out.

So from this, it seems like I have until the subsequent Chirp(s) Available event to transfer my data over CSI. Put another way, the upper limit on CSI transfer time is the time between one chirp ADC sample finishing, and the successive chirp ADC sample finishing.

From SWRA553A - Programming Chirp Parameters in TI Radar Devices

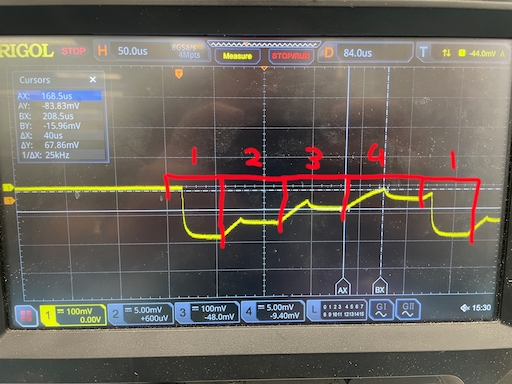

However, in SWRA553A, there is a short note that the time available for data transfer is ramp end time + idle time.

From the provided timing diagram, and given AWR2243 has ping-pong buffers, I understand this to mean the available chirp transfer time is the idle time of the successive chirp + the ramp end time of the successive chirp

Testing

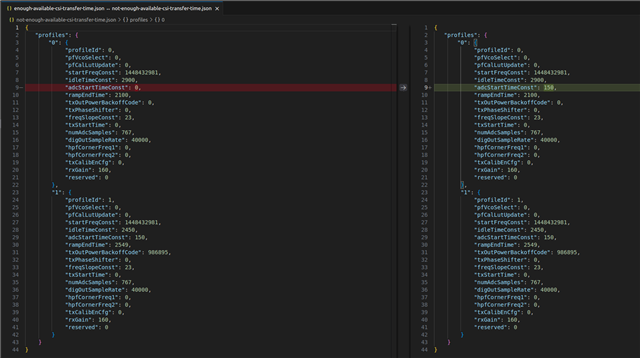

I have tested the available CSI transfer time, and I have found that if I follow the assumption but forward in Programming Chirp Parameters in TI Radar Devices, there is insufficient time to read out the data over CSI, and the AWR2243 generates MSSCPUFAULTs.

However, if I increase the time between ADC sampling ends (Chirp Available events), the CSI transfer seems to work without issues. Note I am not changing the chirp cycle time (idle time before chirp + ramp end time), I am only moving the ADC sampling within the ramp end time to change this timing.

So, as I understand it, the time available for data transfer calculation in SWRA553A should not be relied on, and it more just to demonstrate the need to configure other chirp parameters not accounted for in the ramp timing calculator. It is not meant to be used as a precise reference for available chirp transfer time, except in a very simplified case where ADC timing precisely aligns with the ramp end time

The actual available chirp transfer time is the time between Chirp(s) Available events, which can be increased by increasing idle time, among other chirp parameters

Questions

My questions are

- Am I right in assuming that the available chirp transfer time is the time between successive Chirp(s) Available events, which, if configured for only one chirp per buffer, will be equal to the time between successive ADC samples ending? So I can control the available transfer time by changing the timing of ADC sampling?

- If this is true, then I should be able to increase the available chirp transfer time by increasing the number of chirps to be stored in each of the ping-pong buffers (as per SWRA555A - 2.1.4 Ping Pong Switch Select). Is there any guide to how I can change DSS_REG:ADCBUFCFG4 to allow two chirps to be read into each ping-pong buffer? It doesnt seem to be available through the mmwavelink ICD so I assume the change must be made directly to firmware?

- could you please confirm that the chirp cycle time is composed of idle time first and then ramp end time (as seems to be indicated in Figure 7)?

Thanks very much!