Other Parts Discussed in Thread: AWR2544

Tool/software:

Hi,

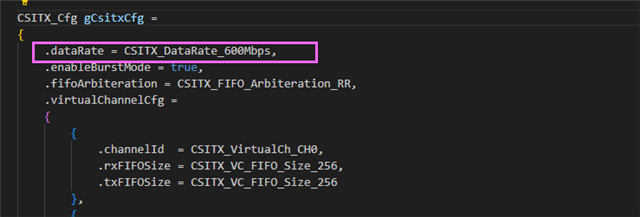

I'm testing with awr2544 CSI-TX OOB demo with GMSL2 MAX96717 serializer chipset. I have followed ECO instruction to make all CSI2 lanes correctly map between awr2544 and gmsl dev kit.

By reading max96717 csi phy counter registers, I confirmed that serializer chip has received csi clock and data from radar chip but it failed to detect a pixel. I have both radar and serializer chip data-type set to RAW8 (0x2A).

Would you please confirm with awr2544 csi-tx full compliance with mipi video pixel mode?

Thanks,

Lam