Tool/software:

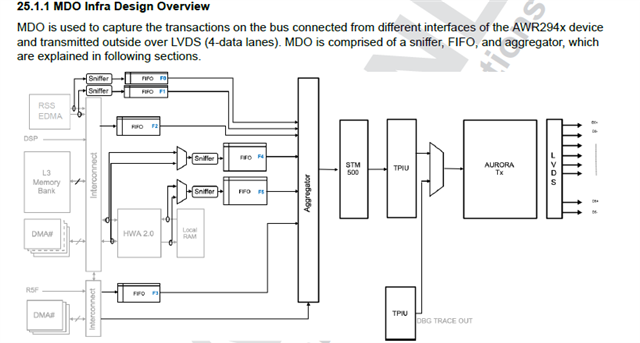

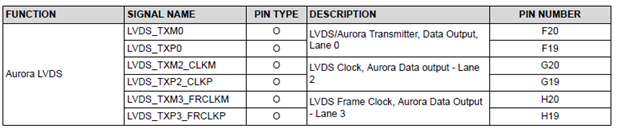

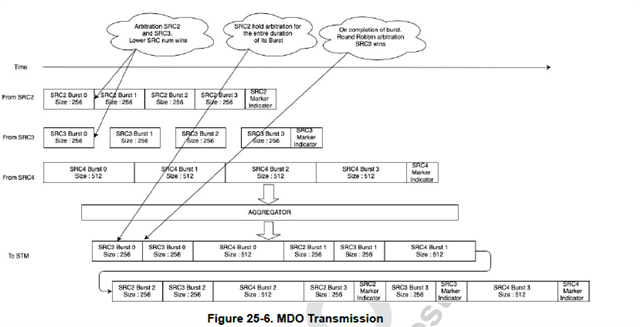

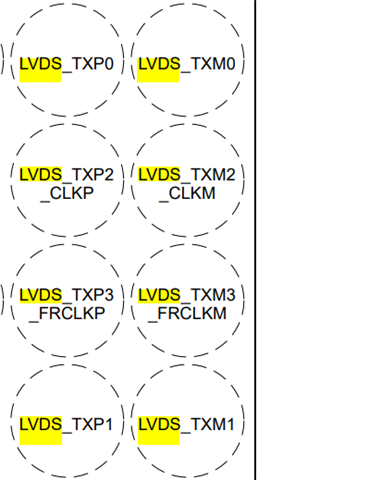

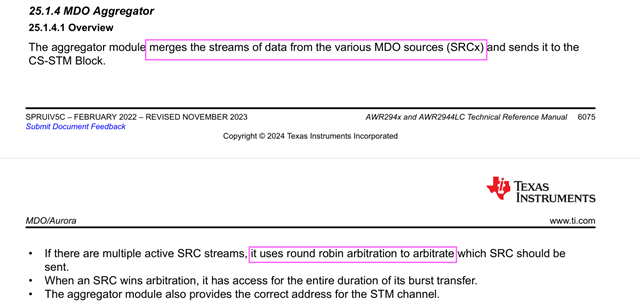

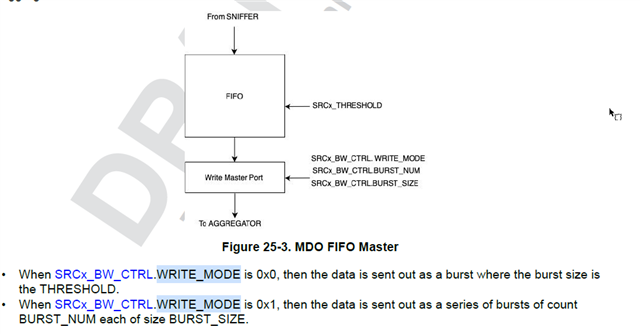

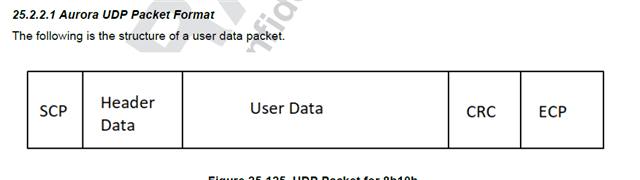

the aurora part in the user manual don't have enough information about the transmit mode , the max size of DMA and each FIFO size , and how the aggregator work , the max size of aurora transmit , and the architecture of the 4 lane LVDS , do TI have more detail information about these parts?