Tool/software:

Hi Team

I have ask a question about tmp102 at TMP102: I2C error reset . In that question, HarryG suggests lowering SCL for more than 30ms to reset the I2C interface of TMP102. We have tried and found that in some scenarios, the I2C interface cannot be reset. We also used sending additional clocks to resolve the I2C deadlock after lowering SCL, but found that SDA continued to send data after sending the clock. At the same time as sending the clock, the host actively raised SDA to simulate NACK, but according to the waveform, TMP102 did not stop sending data after NACK, but continued to send data.

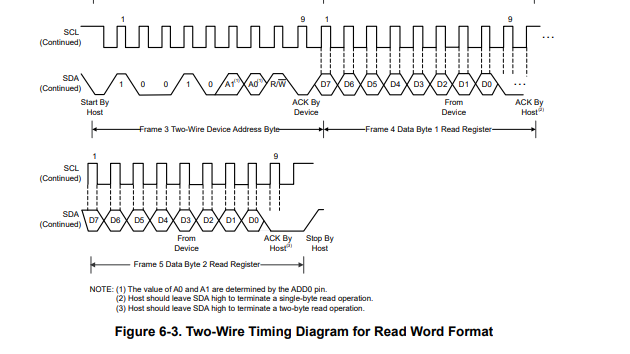

In the datasheet, host should send ack at the end of first byte. I want to know if we send a NACK, will tmp102 release the I2C bus? And why the lowering SCL can't release I2C bus?