Part Number: IWRL6432AOP

Other Parts Discussed in Thread: AWRL6432,

Tool/software:

The manual describes the value of the c_DevClkCtrl parameter in the rl_fecssDevClockCtrl API as follows:

The application can switch the clock source of FECSS based on power state to XTAL clock or Fast clock or can gate the FECSS system clock.

Recommended FECSS clock states:

XTAL Clock – Short idle time.

Fast Clock – Data acquisition mode, calibration or monitoring.

Clock Gate – Long frame idle time.

I have several questions regarding this description, as I would like to clarify the purpose and conditions for setting these values.

Q1) In normal radar control operation, is it correct to assume that selecting the Fast Clock is sufficient,

and that XTAL Clock and Clock Gate are options to consider when aiming to reduce power consumption during FECSS idle time?

Q2) I would like to clearly understand the conditions under which XTAL Clock and Clock Gate can be selected.

The mmwave_dfp_low_api_documentation describes typical use case programming sequences.

In these sequences, the rl_fecssDevClockCtrl API is executed in four states. In which of these states can XTAL Clock and Clock Gate be selected?

-Initialization state

-FECSS Power Down state

-De-Initialization State

-WarmBoot FECSS state

[Reference for programming sequence]

mmwave_dfp_low_api_documentation

{SDK_INSTALL_PATH}/firmware/mmwave_dfp/docs/mmwave_dfp_low_api_documentation/MMWAVE_LINK_DOC.html

Section: In-field Operation

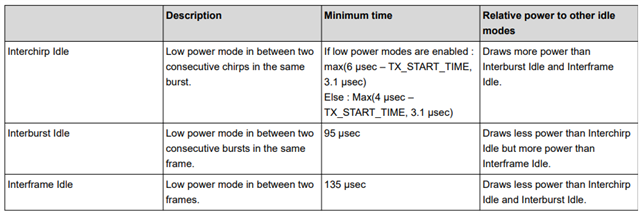

Q3) Could you please explain the time constraints for "short idle time" and "long frame idle time"?

I would like to analyze under what conditions XTAL Clock and Clock Gate can be selected.

Q4) Are there any other prerequisites or limitations when selecting XTAL Clock or Clock Gate?

[Reference]

MMWAVE_L_SDK_05_05_03_00

mmwave_dfp_interface_control_document.pdf

Section 2.3.14 FECSS Device Clock Ctrl API