Other Parts Discussed in Thread: TMAG5170

Tool/software:

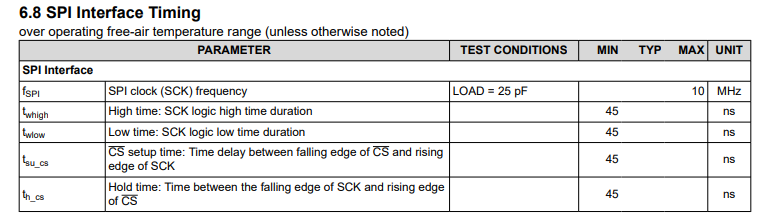

Hi, I'm looking at possibly using the TMAG5170-Q1 in an application with a SPI interface from the LTC6820 operating with a clock frequency up to 1 MHz. Long story short, the duty cycle of the clock signal input to the TMAG5170-Q1 cannot be guaranteed to be 50% or even in the range of 40-60%.

So my question is: Beyond the interface timing requirements called out in the datasheet for this device, are there any duty cycle requirements?

Regards,

B