Other Parts Discussed in Thread: AWRL6844

Hello TI experts,

I would like to double-check the TX sequencing and accumulation behavior for AWRL6844 devices with the following settings:

These cfg lines are captured from TI Radar Toolbox (AWRL6844 SBR) example configuration.

- chirpComnCfg: 50 0 0 128 1 38.25 1

• digOutputSampRate = 50

• digOutputBitsSel = 0

• dfeFirSel = 0

• numOfAdcSamples = 128

• chirpTxMimoPatSel = 1 (TDM-MIMO)

• chirpRampEndTime = 38.25 µs

• chirpRxHpfSel = 1

- frameCfg: 4 12 40000 32 200 0

• numOfChirpsInBurst = 4

• numOfChirpsAccum = 12

• burstPeriodicity = 40000 µs

• numOfBurstsInFrame = 32

• framePeriodicity = 200 ms

• numOfFrames = 0

Assuming 4 TX are enabled in channelCfg, my understanding is:

could you please confirm the following:

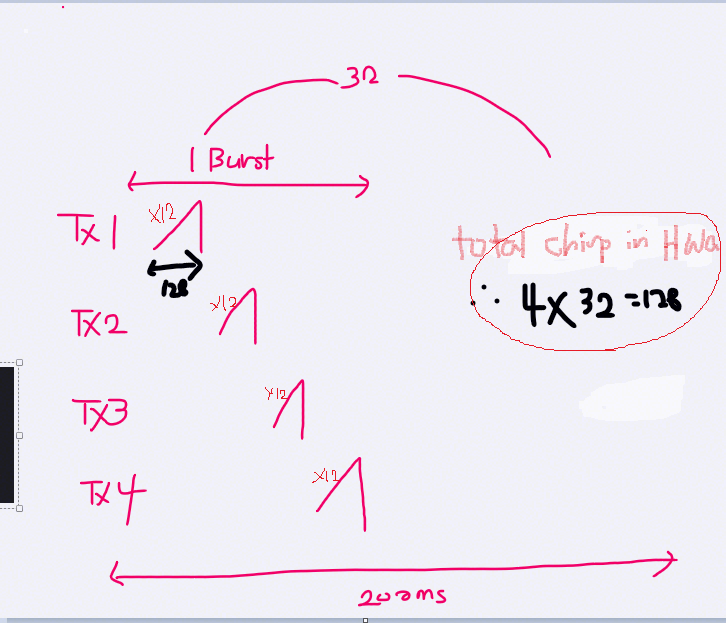

1) With TDM-MIMO and numOfChirpsInBurst = 4, do TX1 → TX2 → TX3 → TX4 each fire exactly once per burst (i.e., one TX per chirp)?

2) For numOfChirpsAccum = 12, is the same chirp physically transmitted 12 times and accumulated in the DFE so that the ADC buffer receives a single accumulated result per chirp?

3) Consequently, is the total number of logical chirps processed by the HWA per frame 4 × 32 = 128 (i.e., accumulation does not increase the chirp count seen by the DSP/HWA)?

I’ve attached a simple sketch illustrating the expected pattern (one TX per chirp, four chirps per burst, 32 bursts per 200 ms frame). Please let me know if this interpretation is correct or if there are any caveats.

Thank you!