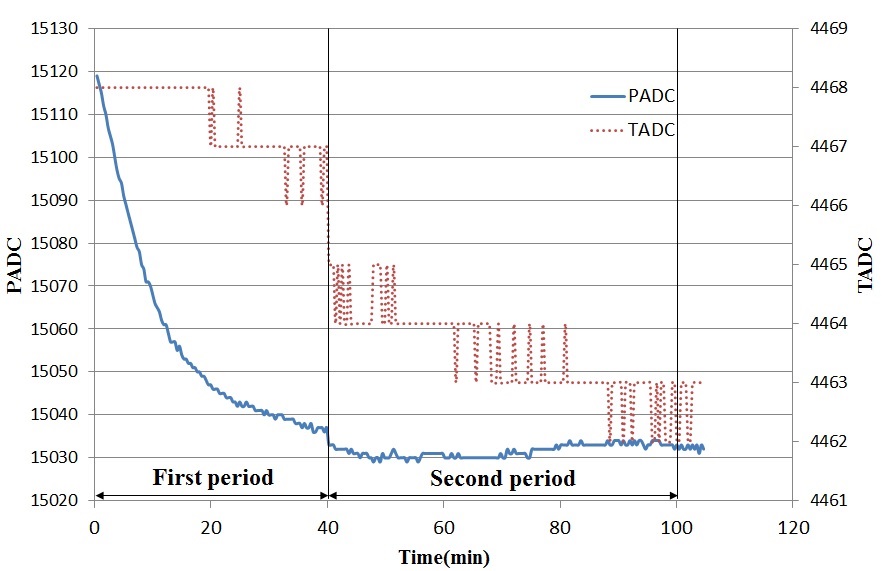

The following figure is the result of PGA900 EVM built-in EXTERNAL BRIDGE with constant temperature at 23.5。C and setting resistance at 246.484 Ω. The first period of TADC variation is from 4468 to 4465 within 0~40 min, respectively. There are 3 difference divisions. When time is range of 40 to 100 min in second period, the difference division is also 3, which result is the same with previously. But the variation of PADC in first stage is decreased from 15120 to 15035(85 difference division), and second stage is almost keeping at 15030. Theoretically, the second stage of PADC value should be decreased the same difference division value from 15035 to 14950. If a single TADC value can’t correspond to a single PADC, even after the compensation, the accuracy of load cell can’t be increased.

- Why the second stage is keeping a constant value when TADC is keeping changed? Is that normal?

- Is the PADC drift can be controlled at a minimum through the register setting or a circuit layout?

- How to evaluate the basic variation divisions in PGA900? Then, I will realize how much difference division is normal.

- What is the highest accuracy through compensation of the PGA900?