Hello i would like to connect this EVM to an FPGA to receive the data measurements and would like to confirm how could be done.

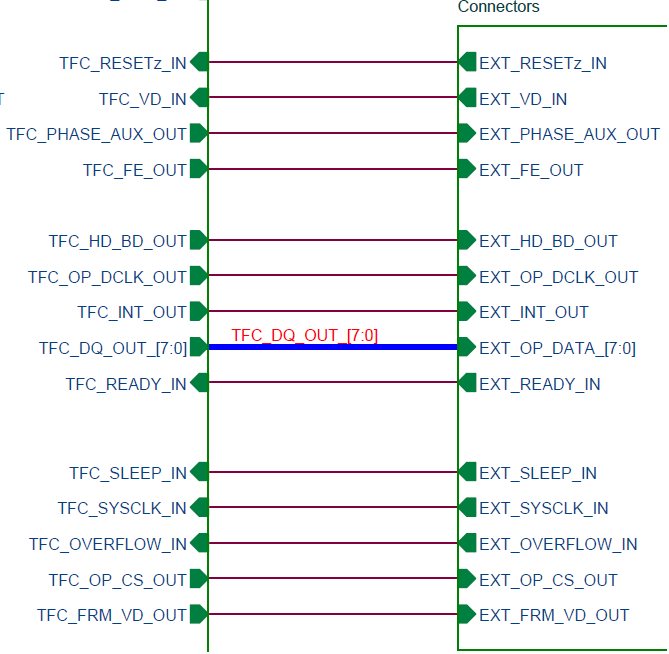

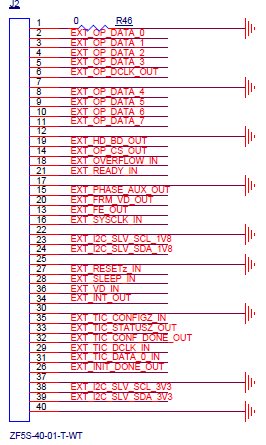

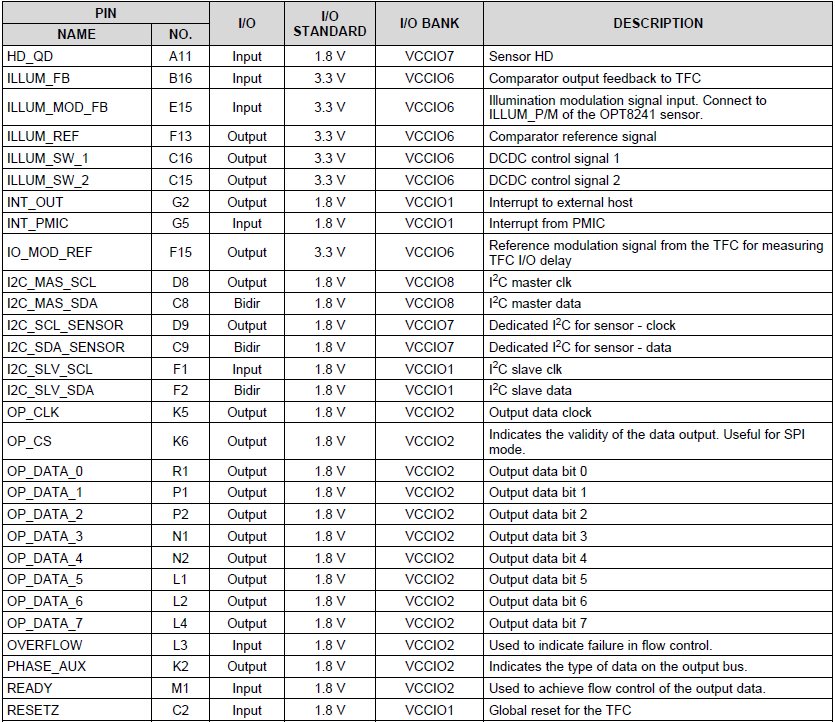

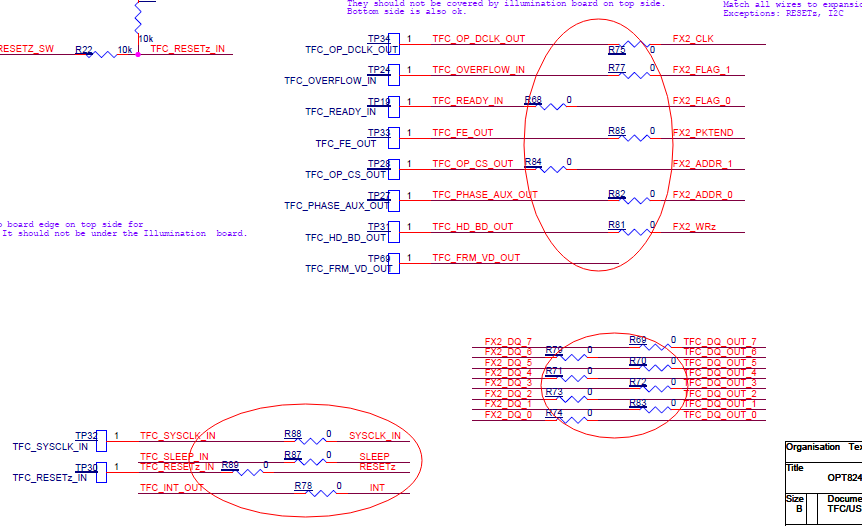

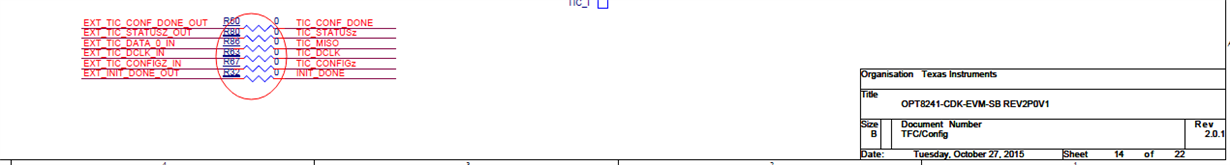

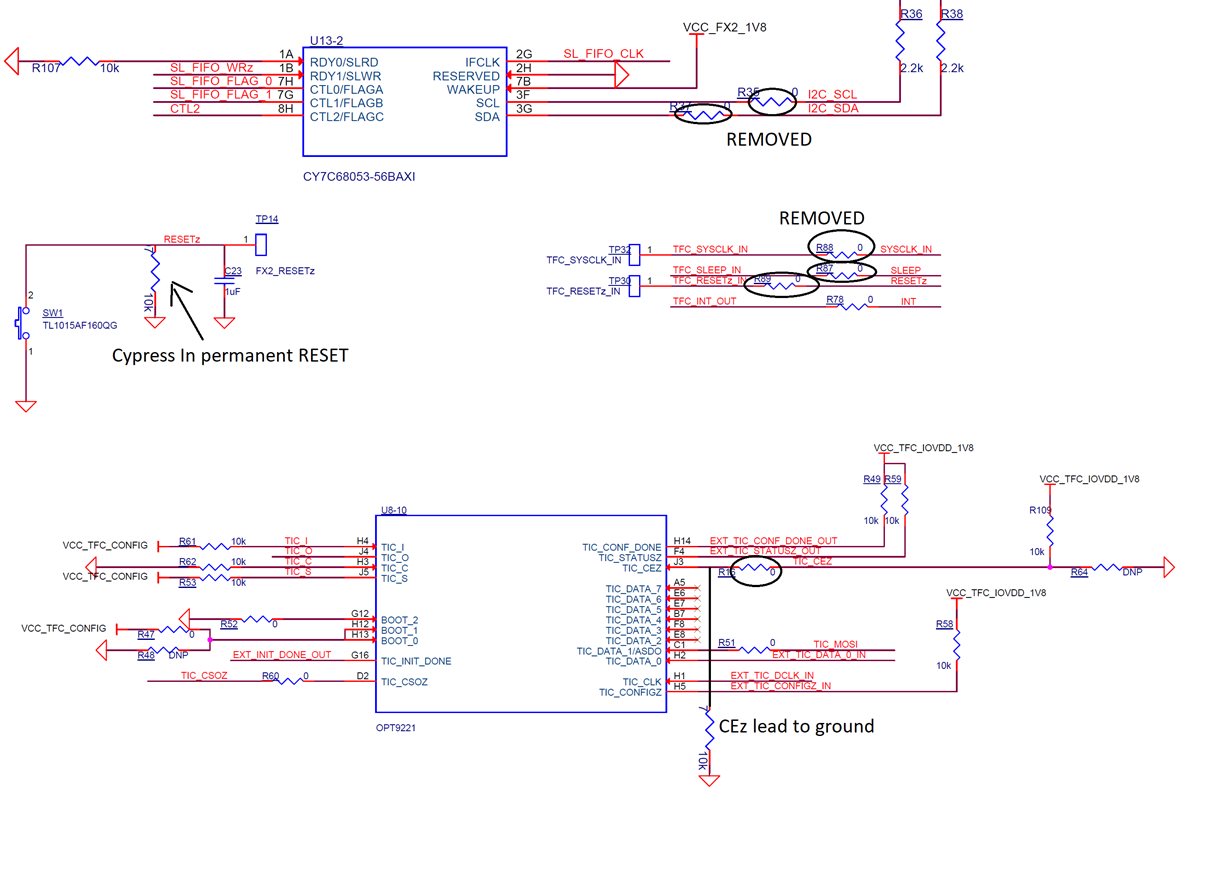

I have seen there is a debug connector (Not mounted) in one side of the EVM and some signals from the OPT9221 are routed to this connector( in schematics the connector is named as ZF5s-40-010T-TW) but I'm trying to figure out what signals corresponds inside the controller because in datasheet they are named differently.

could you provide more info about this connector and their signals?.

Thanks,

Julian.