Other Parts Discussed in Thread: AWR1642, AWR1443

Dear team

Hope you may help my customer, please see the below inquiries.

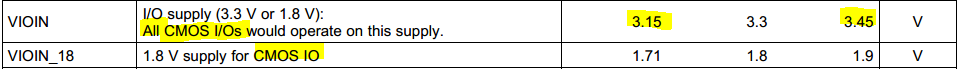

1) The datasheet tells the following regarding VIOIN:

The maximum / minimum values match the 3.3V only. So can I use 1.8V for VIOIN? What are the limits (min/max) in that case?

What is the purpose of VIOIN_18? VIOIN is used to power ALL CMOS I/Os. May you clarify this issue please?

2) There are two RF supplies: VIN_13RF1 and VIN_13RF2, which may be powered by 1.3V or 1V in bypass mode. How does the AWR knows to bypass its internal LDO in case of 1V supply? Should I connect the capacitor to the VOUT_PA in case of bypass?

3) Is there some advantage of supplying VIN_13RF1 and VIN_13RF2 from separate external LDOs? Do these supplies share the same/different LDOs? There is a table 5-3 saying that the 1.3V consumers drawing 2A. May you tell the distribution of this current between VIN_13RF1 and VIN_13RF2 (in case they can be supplied separately)?

4) May you tell the current consumption from each 1.8V supply? Should I supply quiet 1.8V for analog consumers (like Synthesizer, APLL, VCOs and etc.) separately from digital 1.8V consumers (like VIOIN_18DIFF)?

5) Can I omit using the QSPI flash in case I would upload the device’s firmware patch via the SPI on each power-up/reset? In case I can, should I connect the unused QSPI pins to pull-ups/pull-downs? By the way, it can be seen from table 3-1 that AWR1243 doesn’t have QSPI … is it true?

6) Are you planning to remove LVDS mode? Why it is called LVDS/Debug at table 3-1?

7) Table 3-1 says that AWR1243 doesn’t have GP ADC. However, there are 6 GPADC pins according to table 4-1. What is true?

8) According to AWR1243 errata (SWRZ071–May 2017), there is some crosstalk between CSI interface and RF TX (ANA#07). Do you know whether TI is planning to fix this bug? In case they are, may it influence the pinout?

If you can answer the questions above, I will really appreciate it.

Thanks in advance

BR

Shai