Hi TI,

I have done initialisation

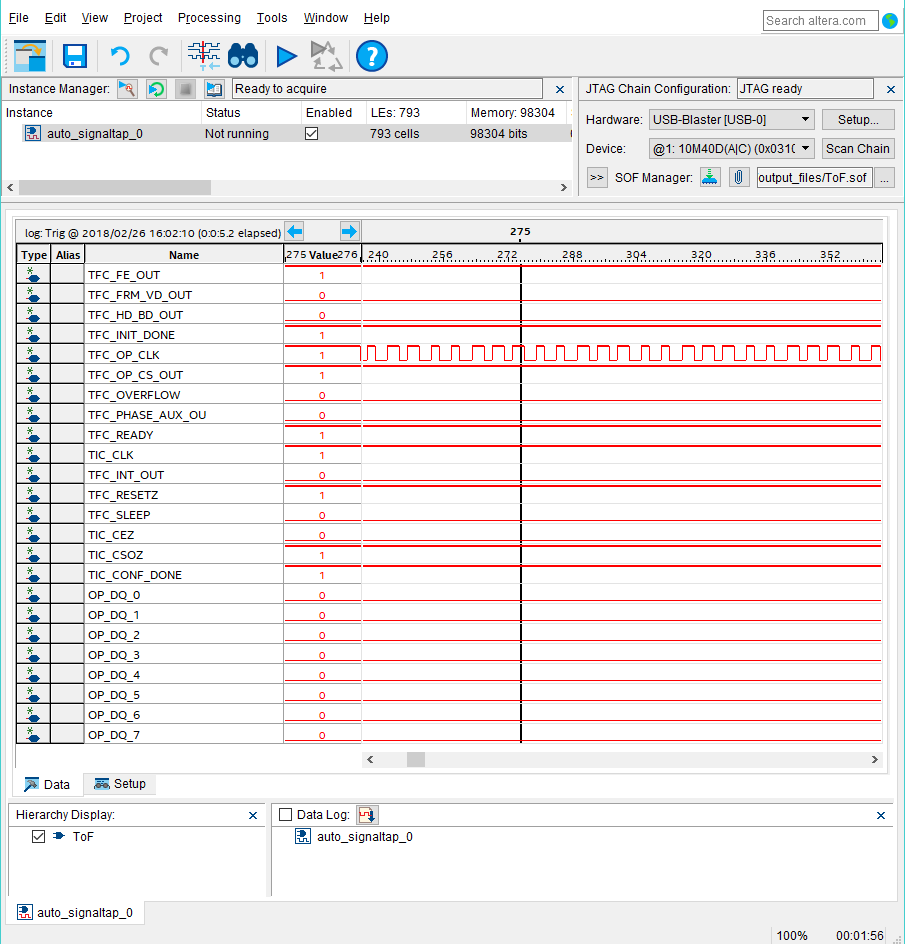

And Int_out pin shows that everything is Ok. I have check all flags in "Register 63h", and everything is ok. Set up pins read/overflow/sleep in 1/0/0 as here

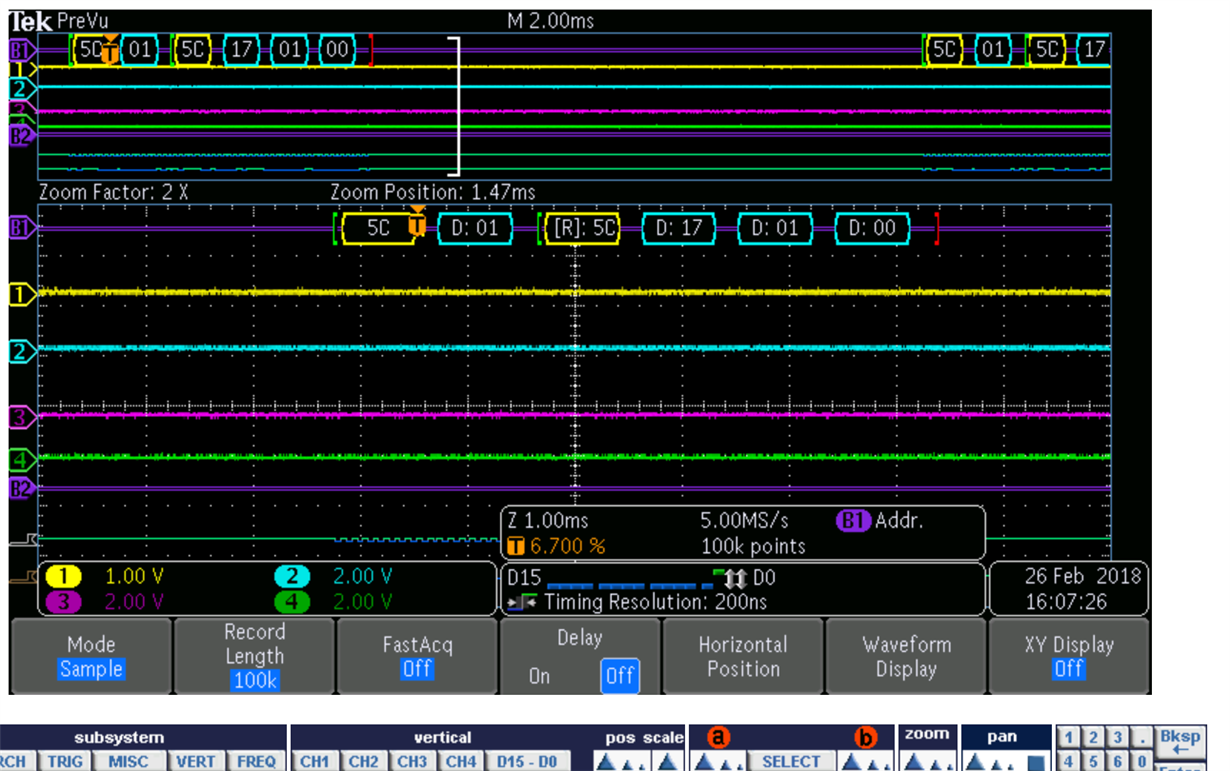

And reg=80h set to 0h (tg_dis) through I2C. I see clock(OP_CLK in 24MHZ, next pic) in my FPGA and continiuos FE_OUT in high level, but haven't any output data. There no any changes in FRM_VD/HD_BD/OP_CS.

May I forgot something to do?