Other Parts Discussed in Thread: LM27313,

I'm using the PGA450-Q1 for distance measurements in a small IoT device. One of our goals is low power. In order to accomplish this, we use a high side P type FET to remove the power from the 7.5V regulator (LM27313).

We are having problems with the EEPROM getting wiped and we suspect the problem lies in the VPWR Ramp Down when we turn the device off. The Application report ( ) would seem to indicate this is where the problem is.

) would seem to indicate this is where the problem is.

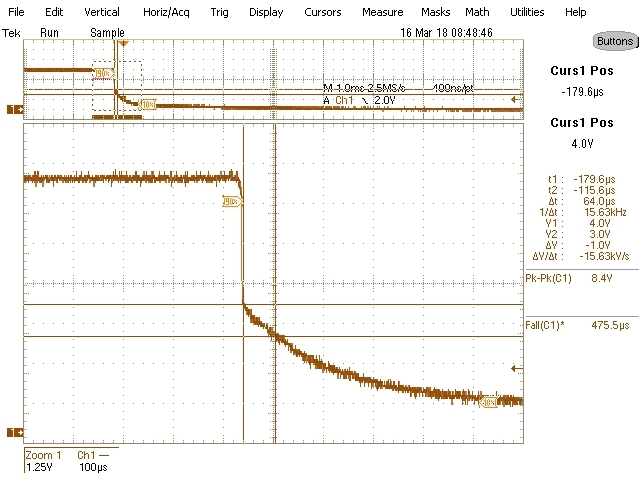

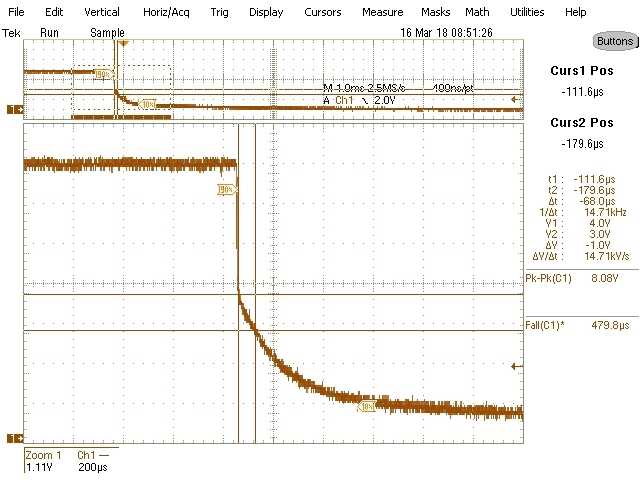

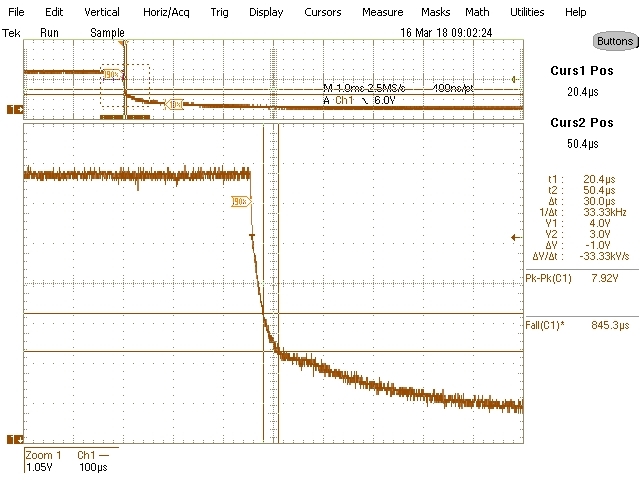

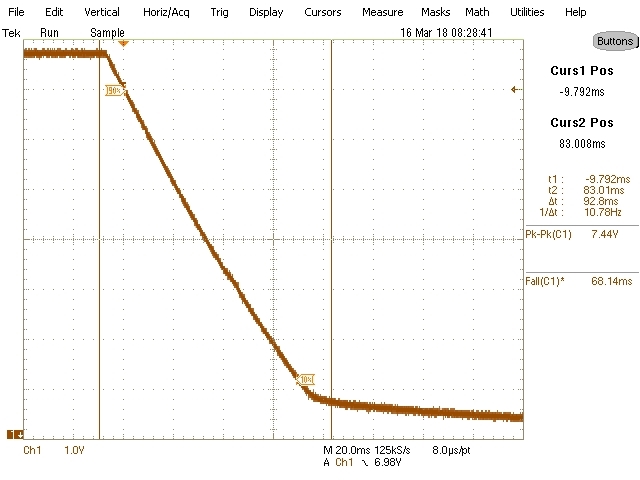

I've done everything to switch the input to the regulator much faster. The problem looks like it lies with the power down time of the 5.2V from VREG. The large 100uF charge capacitor for the transducer can take up to 140ms per 1V between 4V and 3V. As per the application note, this needs to be 1V per 1ms.

Using an external power supply and the Evaluation board, I achieved the same result. Is there a way to discharge VREG in the PGA450 8051 microcontroller so that when we turn off the power, that we can achieve this recommended ramp down. This would indicate the slow issue is part of the PGA itself.

Is anyone else having a problem meeting this recommendation? Has anyone else found an alternative solution.

-Mike