Hi Sir,

We measured power sequence of TI AWR1642 EVM.

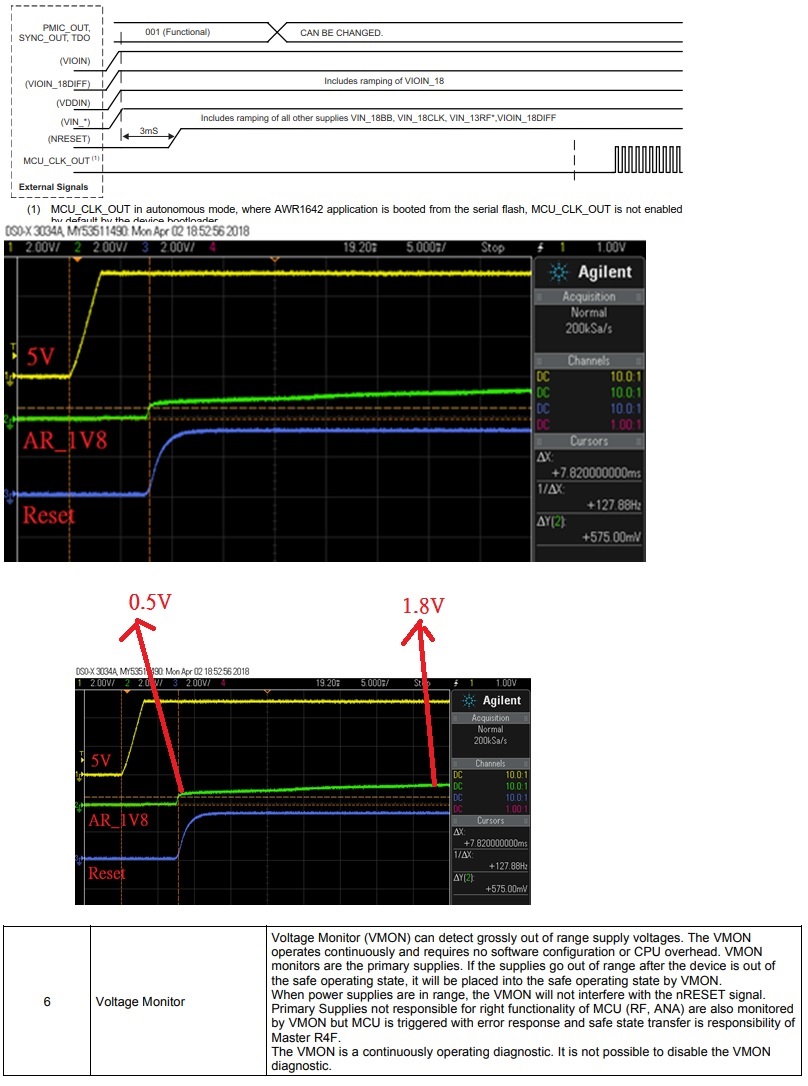

We encountered the AR_1V8 sequence doesn’t meet specification in datasheet.

When NRESET rise high, it should be behind at AR_1V8 about 3ms but it seem not the result we measured in the EVB

Please help to clarify it if we are wrong