Other Parts Discussed in Thread: UNIFLASH, , TPS7A8101, TPS74801,

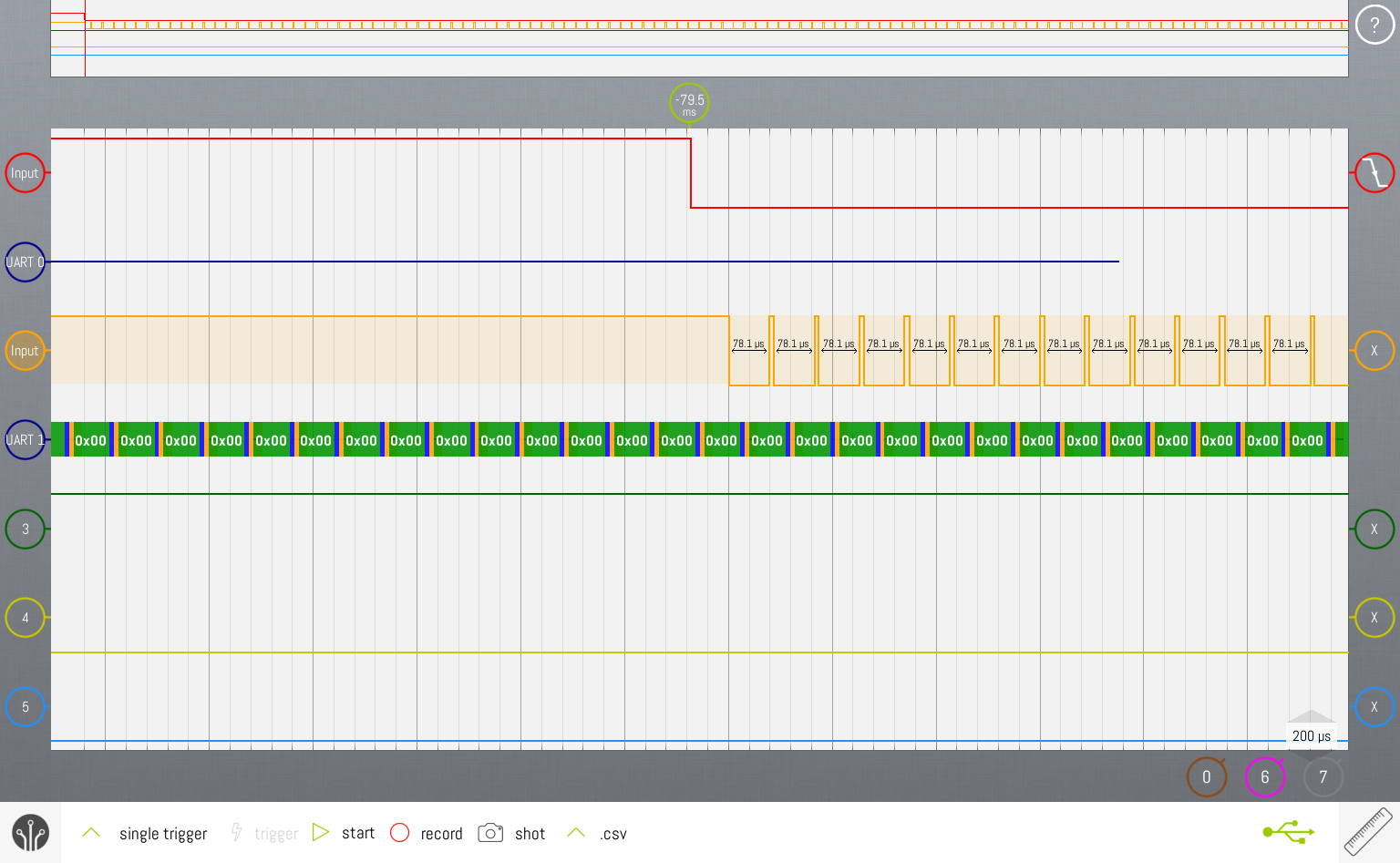

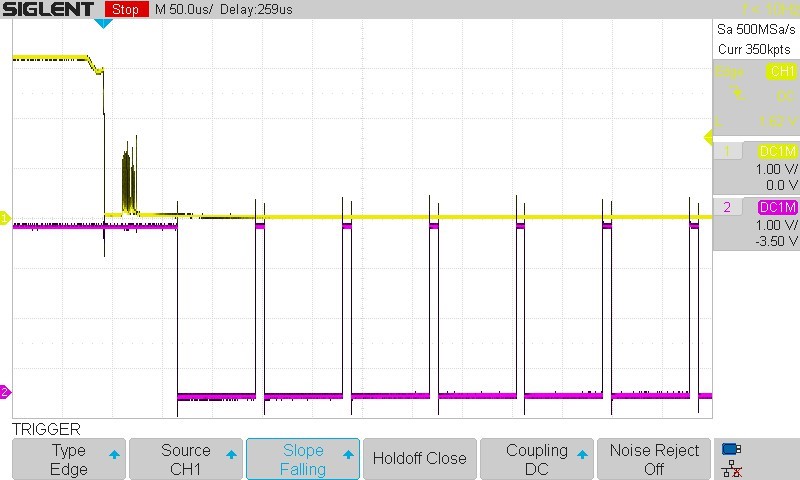

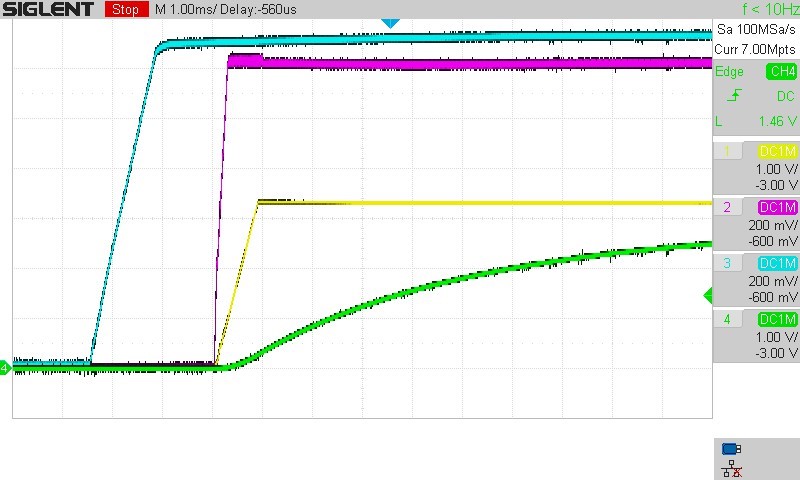

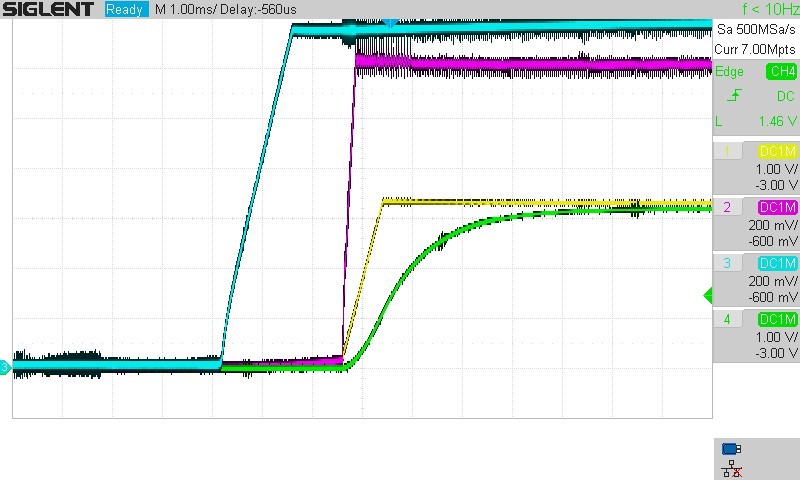

I am seeing the same response from the radio that Daisuke was getting on his customer's board. When Uniflash sends the UART break message, the AWR1243 responds with a never-ending stream of "00" (with proper start and stop bits).

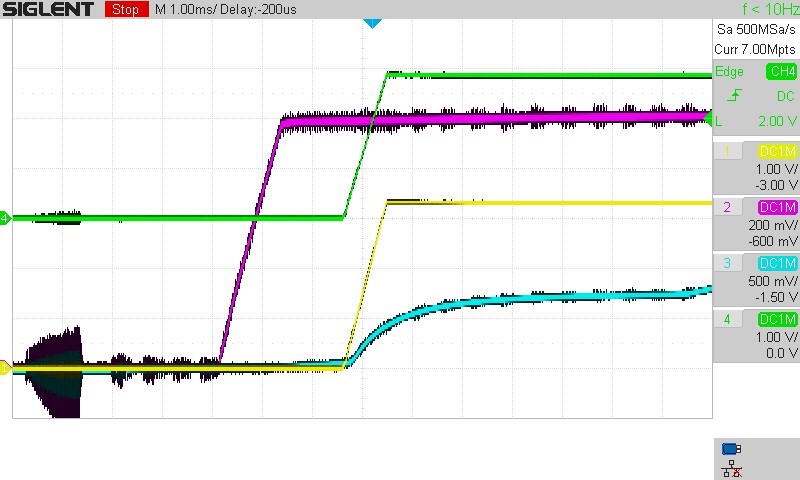

This is my own custom AWR1243 Cascade board, but I am getting the same response from all 4 radios after changing the clock structure to feed 40MHz to all radios directly. The design is directly copied in most part from the TI Boost and Cascade designs.

The SOP jumpers are properly reading "101". I was also concerned that my flash may be incorrect, but upon probing, the AWR1243 isn't even trying to hit the flash. In fact, it is pulling CS low continuously.

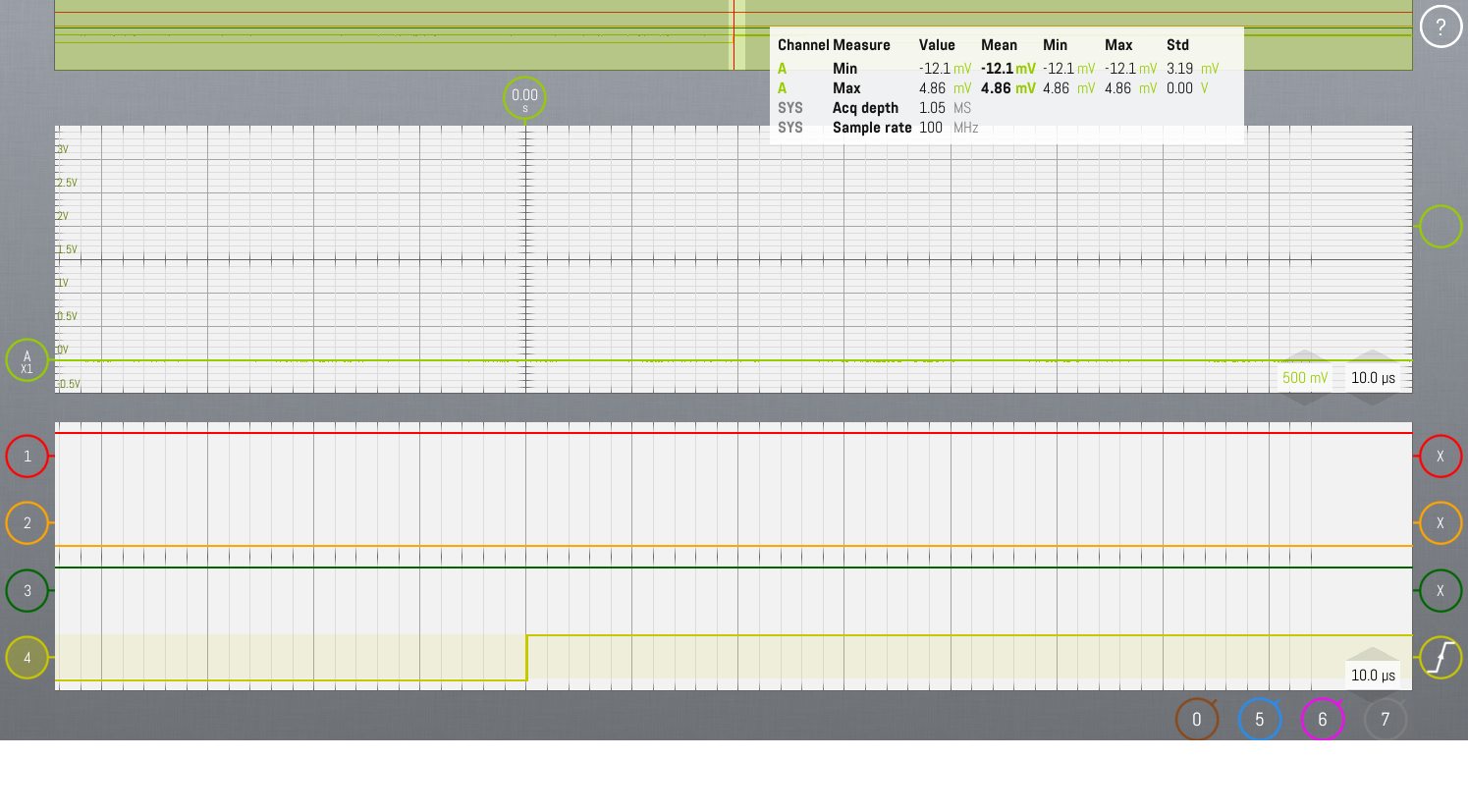

All of the radio power rails appear to be correct. I am using an external LDO for the 1.0V instead of the internal to reduce the heat in the radios. VBGAP measures 0.82V.

I am running out of ideas on what to check next. I have the Boost board and am comparing each signal on my board to it. No luck as of yet.

Thanks for any suggestions on what to try next.