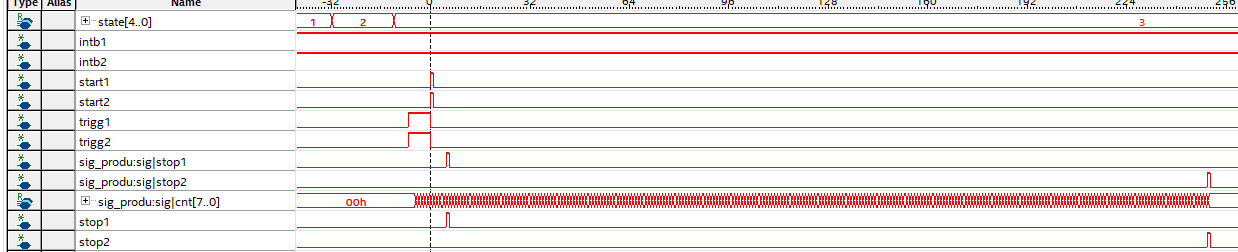

When I use TDC7201, I can not get the intb1 and intb2 signal, they do not change low when I send tdc stop signals, why? What is the problems maybe? My pulse width is 40ns, and I checked the Chapter 6 Specification, I use FPGA to control TDC7201, and I can see trigg signal change low when I give it Start signal. The relevant register use the default values. The reset value is one Stop mode,right? Please reply me. Why can't I get the intb signal rightly? Below is my signal tap ii picture for reference. My start and stop is generated by FPGA. FPGA clock is 40 ns. Thank you!

Thank you!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.