Other Parts Discussed in Thread: PGA450-Q1, , TIDA-00151

Hi,

In order to better understand the behavior of PGA450q1, I have few questions:

1. We want to build a programming and debugging tool for PGA450q1. In order to communicate with a pristine PGA450q1 using SPI, the PGA450q1 must be in a reset state. What will be the process putting the PGA450q1 in a reset state?

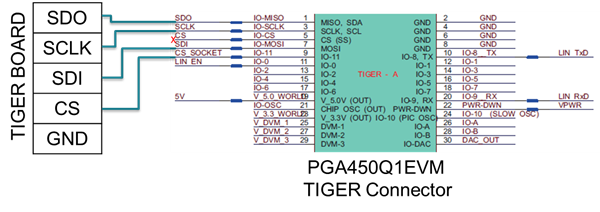

(We are using this socket -> https://www.mouser.com/ProductDetail/adafruit/1280/?qs=GURawfaeGuBaGCXLK7N1zQ%3d%3d&countrycode=US¤cycode=USD

connected to a TIGER board via SPI (SDI, SDO, CS and SCLK), and applying a 12v to vpwr)

2. According to PGA450q1 EVM user manual the soldered PGA450q1 is loaded with dev ram. The dev ram supposed to be wiped every power cycle, but we can see that after power on we can still measure distance or any other functionality of the EVM. Can you please clarify that?

3. On PGA450q1 EVM - is it possible to read the eeprom and other registers of a pristine PGA450q1 which is placed into the socket (not the soldered one)? or the only available functionality is programming the OTP / DEV ram?

Thanks,

Eyal