Hi Team,

We have a timing issue with OPT8320, could you please help? Thanks!

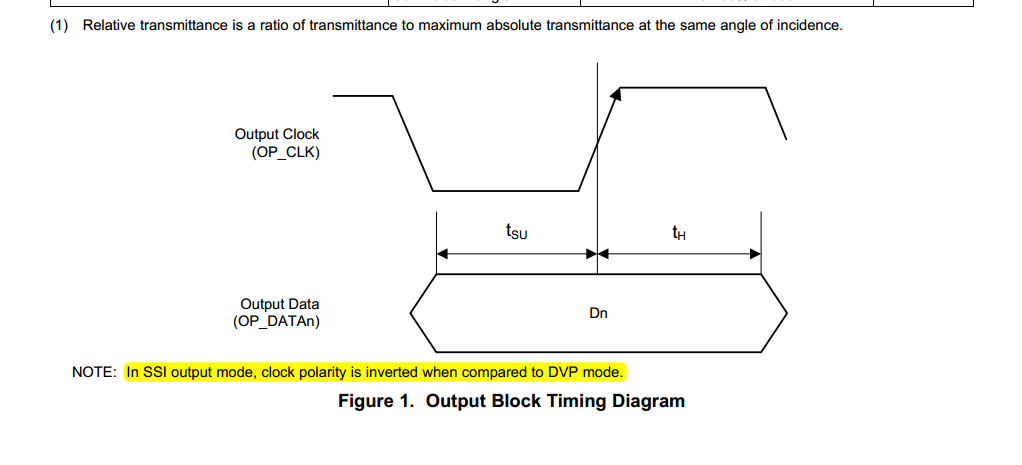

1. What's the time delay between the falling edge of output clock and output data?

2. What's the time delay between the rising edge of output clock and output data?

3. Will the data be sent out on the falling edge or rising edge?

Best Regards,

Hao