Hello, I want to get the ADC raw data from LVDS protocol, and send it to FPGA(xilinx Spartan-6),but I do not know how to set the I/O Standard of the FPGA ,which connect to CSI2 Interface.

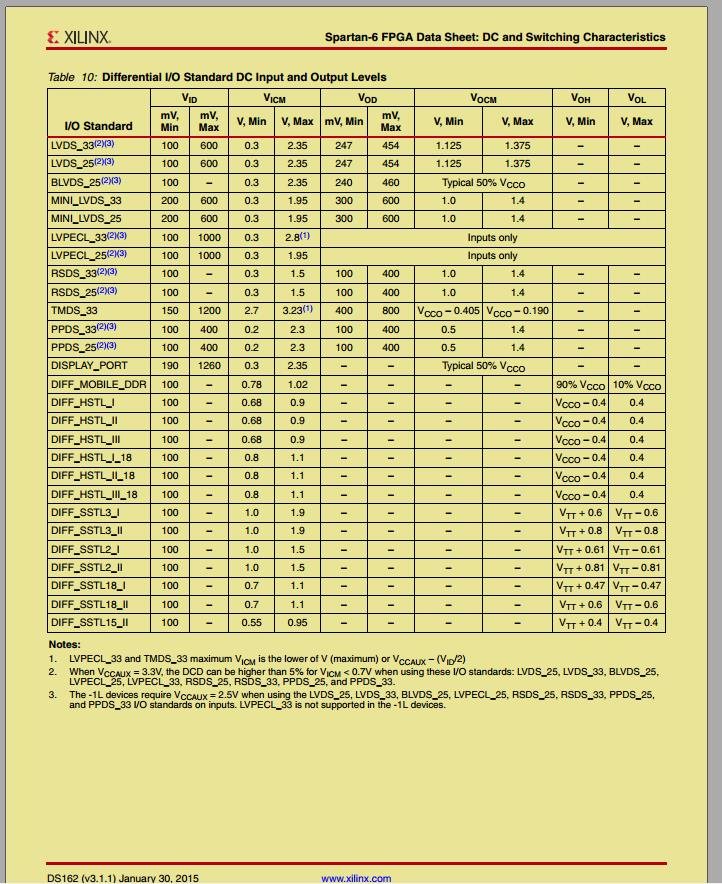

The xilinx Spartan-6 I/O Standard is below, what can I choose? Is there any code demo for FPGA to read the ADC raw data ,thank you.