Hi!

We are designing cascaded radar with 4 AWR1243P.

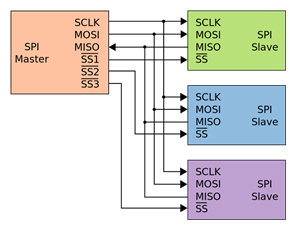

My question is about SPI MOSI output of AWR1243P. We want to use multislave SPI bus for this design like scheme below.

We want to multiplex MISO line by 4 AWR1243P.

It is specified in datasheet that MISO has pull up.

But what is the state of the MISO of AWR1243P when CS of High (chip unselect)? If state is low communication will fail.

Can this state be controlled? Or we need to use separated SPI buses?